Please select your location and preferred language where available.

先端技術トピックス

キオクシアで研究開発を進めている最新技術など参考になるトピックスをわかりやすく解説します。

-

ナノインプリントリソグラフィ(NIL)を用い、その特徴の一つである3Dパターニングの検討を行いました。レジスト材、テンプレート構造、NIL条件、エッチング条件をそれぞれ最適化することで、L/S=4X/4Xnmのサイズの3Dデュアルダマシン構造の形成に成功しました。

-

UVナノインプリントリソグラフィのプロセスマージンを向上させるために、NILアライメントマーク設計ルールとウェハートポグラフィーに応じたパターンカバレッジルールという2つの設計制約を提案導入した。

-

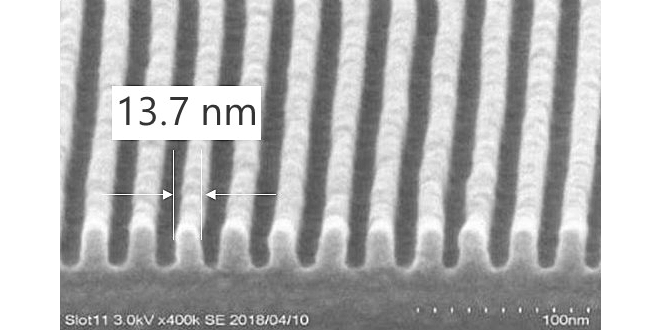

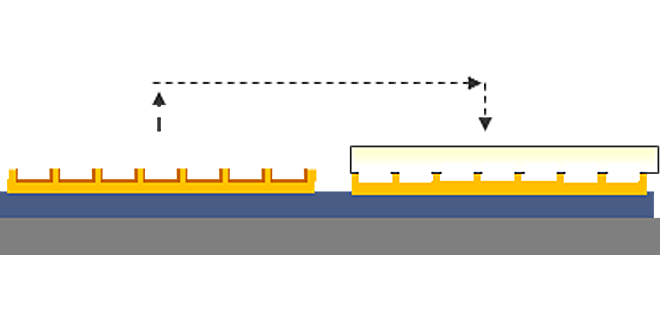

これまで課題であったUVナノインプリントリソグラフィにおける下層レイヤーとの合わせ精度を、合わせマーク別づくり法により解消した。これにより、光リソグラフィでは不可能なハーフピッチ14nmの1回での低コストパターニングの実用化が可能となった。

-

半導体の回路パターンを形成する光リソグラフィプロセスは回路パターンの微細化が進み、ハーフピッチ30nm以下のパターン形成と製造コストの低減に対応するため、ナノインプリント(以下NIL)技術を開発しています。

-

工程数増加や装置コストの増大により、半導体プロセスコストの増大が避けられません。この課題を克服する技術として、低コストで微細パターンの形成を可能にするナノインプリント技術に着目して開発を進めています。

キオクシアの研究部門

豊かで持続的なデジタル社会の実現のため、メモリ技術の革新により、絶え間ない技術探索とその社会実装を目指します。

当社が世界に先駆けて開発した3次元フラッシュメモリ「BiCS FLASH™」の研究開発と量産化の橋渡しを行っています。