Please select your location and preferred language where available.

3次元フラッシュメモリ「BiCS FLASH™」とは

キオクシアは2007年に世界で初めて 3次元フラッシュメモリ技術を発表しました。コスト低減の実現につながったイノベーションポイント、さらなる大容量化への取り組みをBiCS FLASH™の解説とともにお届けします。

フラッシュメモリの大容量化

社会のデジタル化が急速に進み、保存すべきデータ量は爆発的な勢いで増えています。そのため、1つのフラッシュメモリの中に、よりたくさんのデータを保存する「大容量化」が必要とされています。

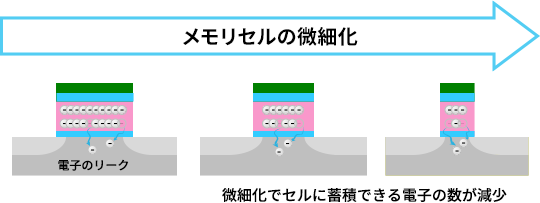

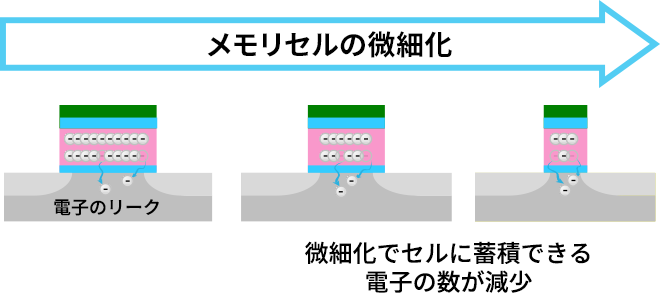

この大容量化を実現するために、キオクシアでは1つのメモリセルが占める面積をできるだけ小さくして、1つのフラッシュメモリの中に、できるだけたくさんのメモリセルを搭載するメモリセルの微細化技術を開発し、15nm(ナノメートル*1)の製品化を実現しました。しかし、微細化技術にも限界があり、例えばメモリセルどうしが近いことで、意図しない電流が流れてしまう現象や、図1のように、 1つのメモリセルに蓄積される電子の個数が微細化により減少することで、ごくわずかな電子のリークがデータの安定性に影響を与えるようになりました。

- 1nm(ナノメートル)は1メートルの10億分の1

BiCS FLASH™の誕生

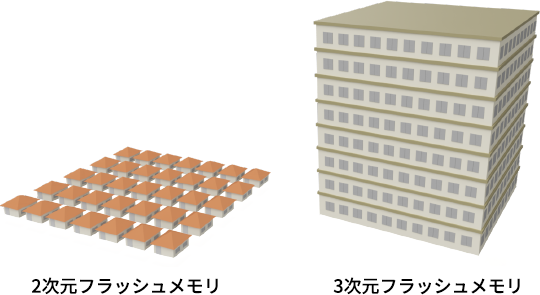

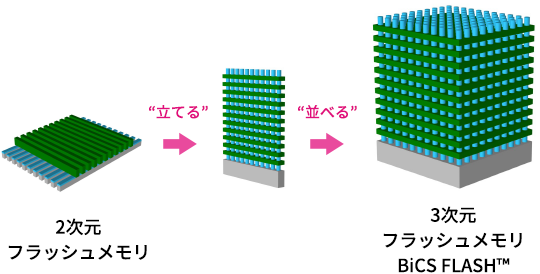

そこで生まれたのが、平面構造のフラッシュメモリを上に積み上げていくことで、面積あたりのメモリセルの数を増やすという発想でした。建物にたとえるならば、10人しか住めなかった平屋を、5階建てのマンションに改築することで、同じ土地面積でも50人住めるようにする、ということです。つまり、積み上げれば積み上げるほど、土地の面積は増やさずに、たくさんの人が住めるようになります(図2)。

しかし同時に、新たな課題も生まれました。平面構造のフラッシュメモリを、下から順番に積み重ねていくと、メモリ層を1層追加するたびに、フラッシュメモリの構造を作るための手間も同時に増えていきます。つまり、積み上げれば積み上げるほど、お金がかかってしまいました。

そこでキオクシアでは、この製造コストの問題を解決するために、3次元フラッシュメモリBiCS FLASH™を2007年に発表しました。

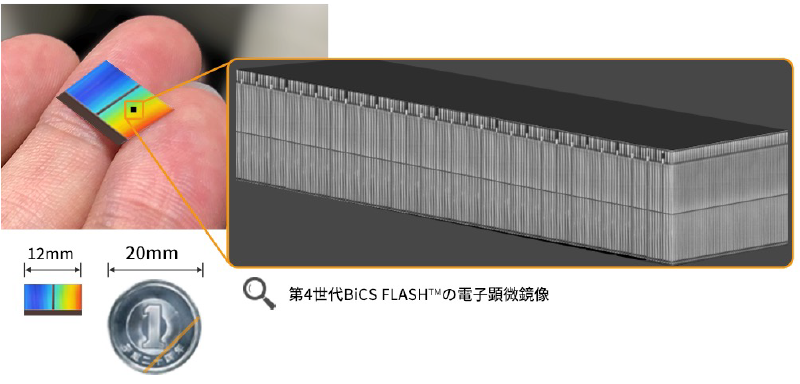

2007年にBiCS FLASH™の「一括加工技術」のコンセプトを学会発表して以降、2015年に48層、2018年には96層、2020年には112層、2022年には162層のBiCS FLASH™を製品化し、様々な製品に使用されています。

BiCS FLASH™の技術

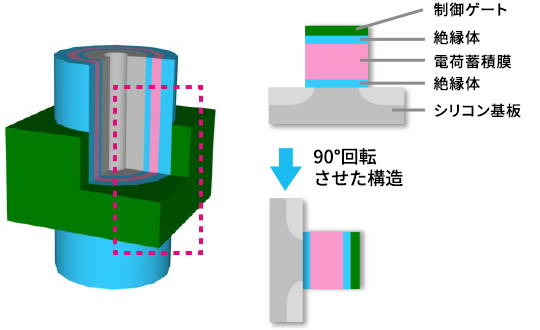

BiCS FLASH™の一括加工技術を説明します。BiCS FLASH™では、制御ゲートの役割を果たす板状の電極(図4の緑色の板)と絶縁体を交互に積み上げ、面に対して垂直に一気にたくさんの穴を開けます(パンチ)。次に、板状の電極に開けられた穴の内側に電荷蓄積膜(ピンク色の部分)と柱状の電極(グレーの柱状の構造体)を埋め込み(プラグ)ます。すると、板状の電極と柱状の電極の交点が1つのメモリセルになります。

BiCS FLASH™のメモリセルを拡大してみます(図5)。BiCS FLASH™のメモリセルでは、円柱の中心を通る電極(グレーの構造体)と、ピンクの電荷蓄積膜とで電子がやりとりされます。

このように、1層1層下からメモリセルを積み上げていくのではなく、まずは、板状の電極を積み上げ、それらを貫通する穴を開けて電極を通し、一気にすべての層でメモリセルを作ることで製造コストを低減する画期的な技術がBiCS FLASH™です。

さらなるメモリ大容量化に向けて

さらにキオクシアでは、メモリの大容量化のために、積層数を増やすための研究開発を10年以上続けています。2023年3月時点で200層を超える積層数を実現させています*2。ナノメートルの世界において、板状の電極を積み上げそれらを貫通する穴を開け電極を一気に貫通させることを想像すると、このBiCS FLASH™は非常に緻密で繊細な技術だということがわかります。

*2 2023年3月30日プレスリリース