Please select your location and preferred language where available.

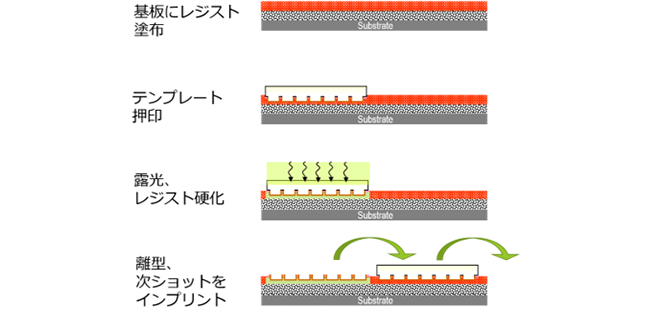

UVナノインプリントリソグラフィ(Nanoimprint Lithography、以下NILと表記)は、図1に示すようにマスクとシリコン基板を直接接触させて、基板上に原版パターンを転写するプロセスです。

光リソグラフィとは異なり、レジストパターンはテンプレート上の原版パターンと同じスケールでウェーハ上に形成されます。テンプレートパターンは、もともと電子ビームリソグラフィで作成されたもの、10nm台の寸法のパターンが形成可能です。

過去に報告されているように[1-3]、NILによって光露光の解像限界を超えるハーフピッチ14nmのラインアンドスペースパターンが1回のパターニング工程にてシリコン基板上に形成されます。本発表では、NILの下層パターンとの重ね合わせ性能に関する報告を行いました[4]。

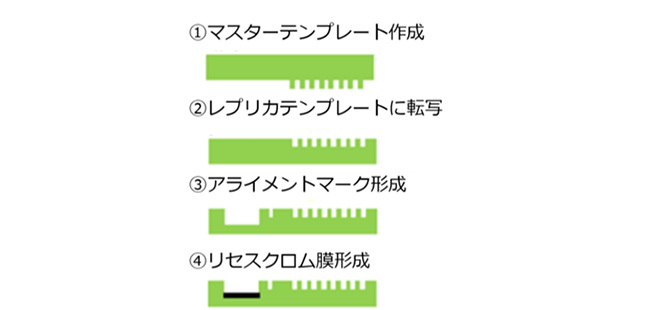

NILは基板への位置合わせ精度2nmを達成していますが、ハーフピッチ14nmのような特に微細なパターン形成に特有の問題がありました。それは、テンプレート製造工程の設計制約により、Siウェーハへのテンプレートの位置合わせ(アライメント)においてアライメント信号が弱くなり、アライメントの再現性が悪くなることです。今回私たちは、テンプレート表面に形成するNILのアライメントマークの製造工程を図2に示した本体パターンとアライメントマークの別形成プロセスを使うなどの工夫をすることでアライメント信号を高め、実際に図3に示すようにシリコン基板への位置合わせ(誤差<3nm)とインプリントが出来ることを示しました。

さらに、デバイス構造を模擬した複数種類の基板を用いて十分なアライメント信号強度、および位置合わせ精度が得られることを実験的に示しました。これは、ハーフピッチ14nmシングルパターニングと実使用に即した下地パターンとの高精度のアライメントによる先端メモリデバイス製造のコスト低減の実現に道を拓く成果です。

本稿は、文献[4]から図面等一部抜粋&再構成したものです。

文献

[1] T. Nakasugi et al., “Half pitch 14 nm direct pattering with Nanoimprint lithography”, 2018 IEEE International Electron Devices Meeting (IEDM), IEDM Technical Digest 2018, pp. IEDM18-265-268.

[2] T. Kono et al., “Half pitch 14nm direct patterning with Nanoimprint Lithography”, Proc. SPIE, 2019, 10958, 109580H.

[3] T. Nakasugi et al., “Multi-field imprint technology: enabling the productivity enhancement of nano-imprint lithography”, J. of Micro/Nanopatterning, Materials, and Metrology, 21(1), 011002 (2021).

[4] K. Fukuhara et al., “Evaluation of alignment accuracy for nano-imprint lithography”, SPIE Advanced Lithography + Patterning 2022 On Demand, May 23-29, 2022.