Please select your location and preferred language where available.

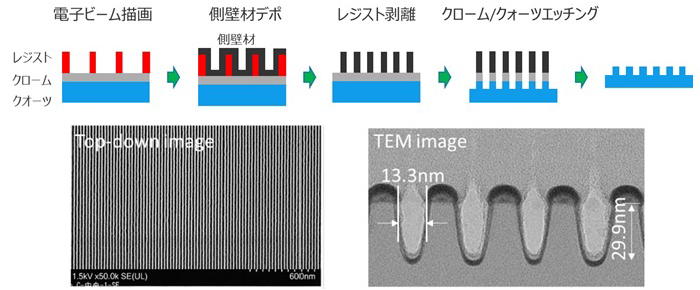

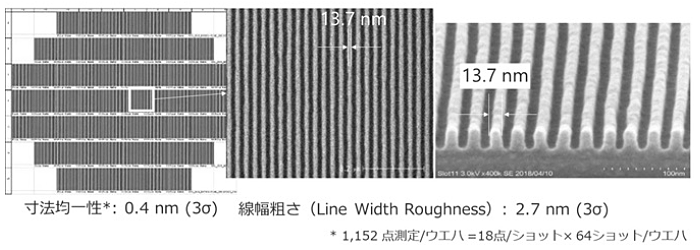

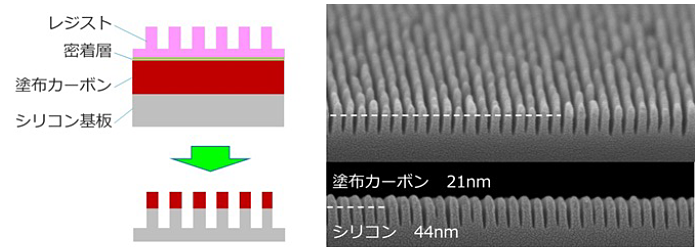

半導体の回路パターンを形成する光リソグラフィプロセスは回路パターンの微細化が進み、ハーフピッチ30nm以下のパターン形成と製造コストの低減に対応するため、ナノインプリント(以下NIL)技術を開発しています(当ホームページの『次世代リソグラフィプロセス技術 ~ナノインプリント技術~』ご参照)。今回我々は自己整合的な側壁プロセスによる14nmハーフピッチテンプレートを開発し(図1)、ナノインプリントリソグラフィによりウェハ上に14nmハーフピッチのレジストパターンを形成し(図2)、シリコンウエハ上に一括パターニングすることに成功しました(図3)。これによりNILが将来の微細デバイスに向けた低コストな次世代リソグラフィプロセスの有力候補であることを実証しました。

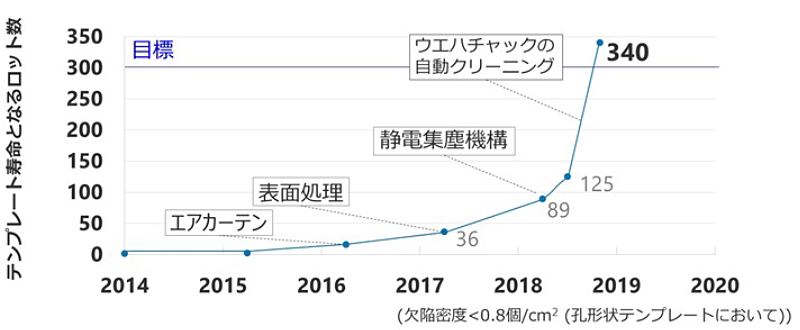

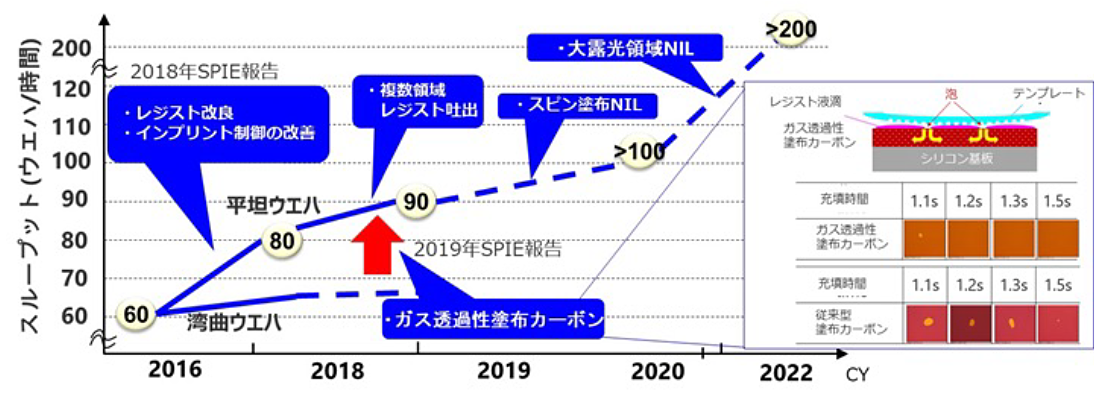

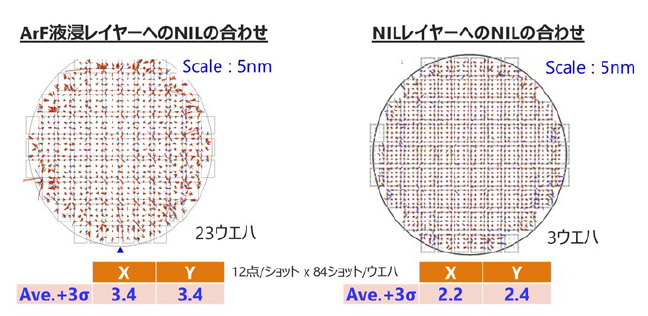

またNILはウェハとテンプレートが接触するプロセスであることから、テンプレート破壊防止(テンプレート寿命向上)や押印時のレジスト充填時間短縮(スループット向上)、押印時の歪み抑制(合わせずれ向上)が課題となります。我々はパーティクル除去技術によるテンプレート長寿命化(図4)、レジスト充填時の泡抜けを促進する材料 (レジスト材料、ガス透過性塗布カーボン)プロセス技術によるスループット向上(図5)、複雑な高次歪みを補正する技術による合わせずれ精度向上(図6)を実証しました。

本技術については2019年2月に米国サンノゼで開催された国際会議“SPIE Advanced Lithography”において発表を行いました[1]。

参考文献

[1] T Kono, M. Hatano, H. Tokue, H. Kato, K. Fukuhara, and T. Nakasugi, “Half pitch 14nm direct patterning with Nanoimprint Lithography”, Proceedings of SPIE - The International Society for Optical Engineering, 10958 (2019)