Please select your location and preferred language where available.

Technology Topics

Introducing the latest technologies being researched and developed at KIOXIA Corporation and various use cases of flash memories.

-

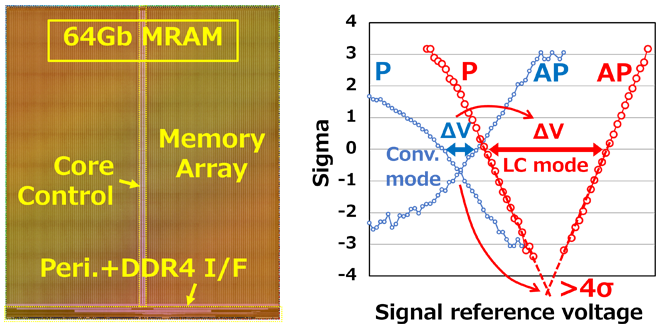

The world’s highest density 64Gbit cross-point MRAM chip with 1Selector-1MTJ cell has been developed. The work presents a novel reading scheme, which enables a high-speed 3ns read pulse and a read margin of over 4-sigma, while addressing read disturbances using the smallest cell size to date.

-

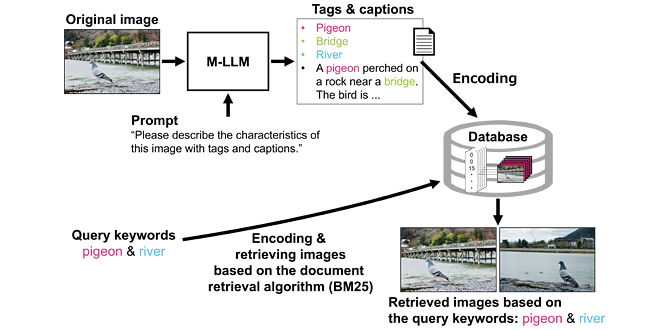

We have developed an image retrieval system that utilizes a multi-modal large language model and a document retrieval algorithm. We have confirmed the performance improvement in the keyword-based retrieval scenario.

-

As the number of multi-level increases from MLC, TLC and QLC, while the memory density can be increased, the number of reads increases and random access deteriorates. We reported on a new multi-level coding method that reduces the number of reads and enables high-speed random access while maintaining a high memory density by sharing data among multiple memory cells.

-

We are evaluating Compute Express Link™(CXL) memory as external memory for GPUs. We have demonstrated GPU graph processing speeds close to using the host DRAM when the CXL memory latency is under a few microseconds. This indicates the possibility of replacing DRAM with low-latency flash to achieve a cost-effective system.

-

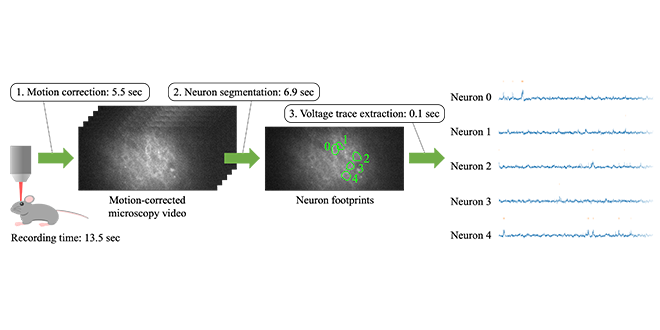

We are developing high-speed microscopy image processing methods leveraging SSDs. One of them is a method able to extract neural voltage from microscopy video in real time, and we presented it at the International Conference on Bioinformatics and Biomedicine (BIBM) 2023.

-

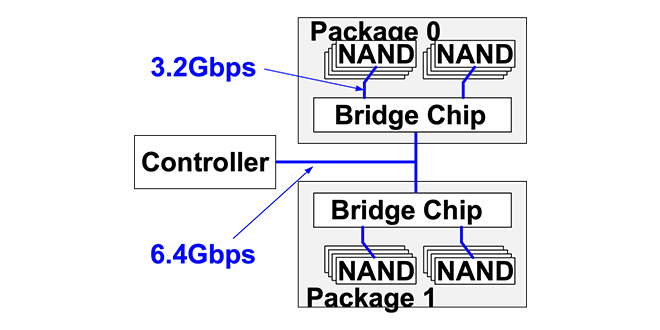

We have developed a Bridge Chip provides twice the speed of existing NAND interfaces even with multiple packages on each PCB channel. A NAND Flash Memory Multi-Chip Package incorporating both eight 1-Tb NAND dies and developed Bridge Chip can operate at 6.4Gbps/pin.

-

We developed the accessible frameworks for developing and evaluating retrieval-augmented large language models.

-

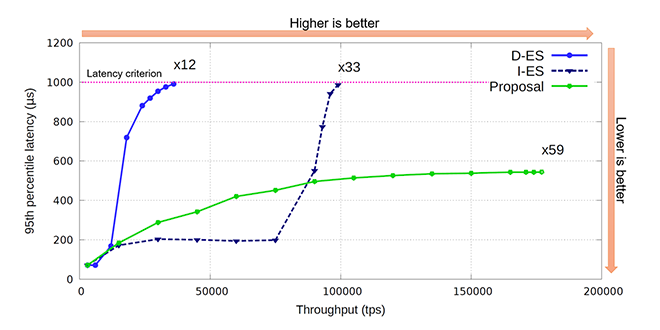

The erase operation of flash memory is one of the causes of performance degradation in SSDs. We have developed an efficient erase technology for low-latency flash memory-based SSDs and achieved a significant performance improvement in a database application evaluation.

-

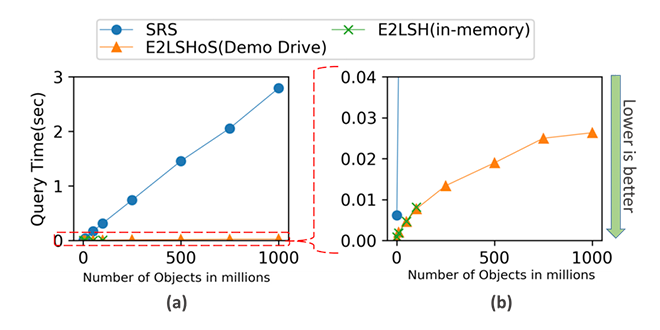

Locality Sensitive Hashing (LSH) is an approximate nearest neighbor search method widely used for big data search and retrieval. By effectively introducing flash memory and developing a new algorithm, we have improved LSH and achieved significant performance improvement by reducing the overhead of computation and external storage access without increasing the main memory.

-

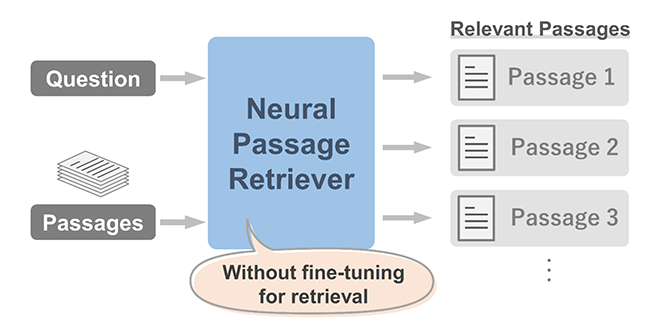

We developed a zero-shot passage retrieval method which employs a pre-trained neural language model without fine-tuning for retrieval. The proposed method achieves almost comparable performance to state-of-the-art passage retriever when a named entity in a question is a dominant clue for retrieval, where conventional neural retrievers have struggled to perform.

-

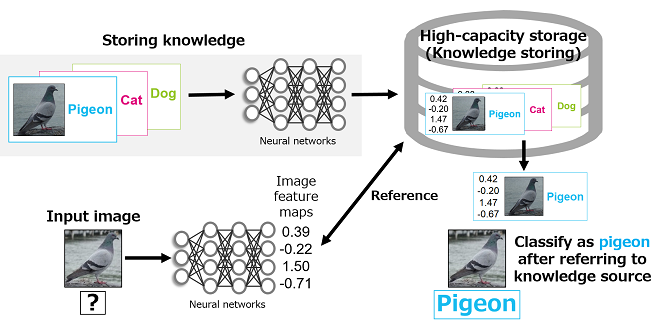

We developed a Memory-Centric AI-based image classification system that utilizes high-capacity storage to enable knowledge expansion while avoiding catastrophic forgetting. It improves explainability of AI by retaining the reference images used for classification.

-

November 30, 2022 Frontier Technology R&D Institute (System Technology)

We developed the technique for avoiding false-lock points induced by PAM4 signaling by switching the comparator mode between NRZ mode and PAM4 mode according to the state of the CDR operation, and confirmed the effectiveness of proposed technique.

-

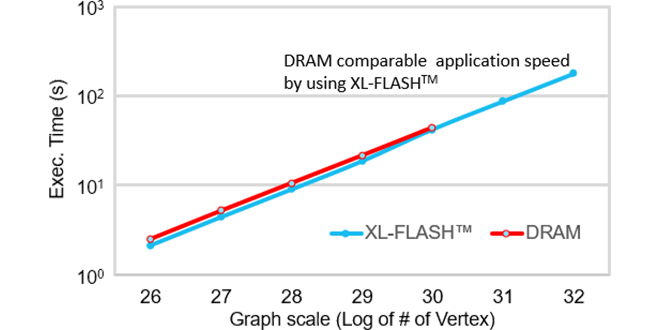

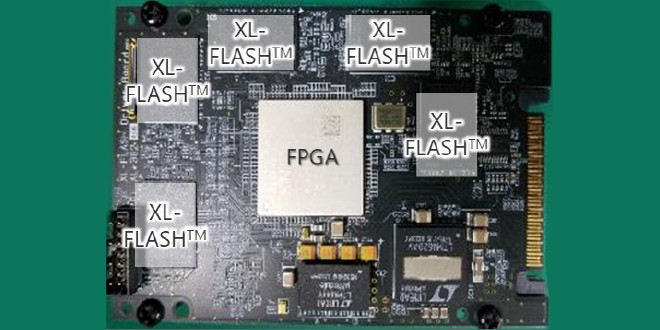

We introduced high-speed flash memory (XL-FLASH™) and developed a new access method for it, achieving the equivalent speed as keeping all graph data in DRAM. This enables high-speed processing for very large-scale graph with flash memory at lower cost than DRAM.

-

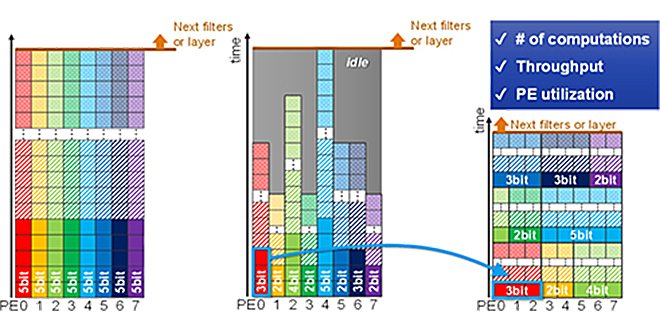

We have developed not only a filter-wise quantization algorithm which optimizes the number of weight bits for each one of tens or thousands of filters on every layer but also the dedicated accelerator. With these algorithm and hardware architecture, the inference time can be reduced while maintaining recognition accuracy.

-

We demonstrate capability of replacing DRAM for a key-value store database using XL-FLASH™, which has lower bit cost and larger capacity than DRAM. In order to evaluate the possibility of DRAM replacement using XL-FLASH™, we have developed XL-FLASH™ demo drive, and demonstrated the evaluation result that the database using DRAM and the database using XL-FLASH™ have equivalent performance in read access-dominated situation.

-

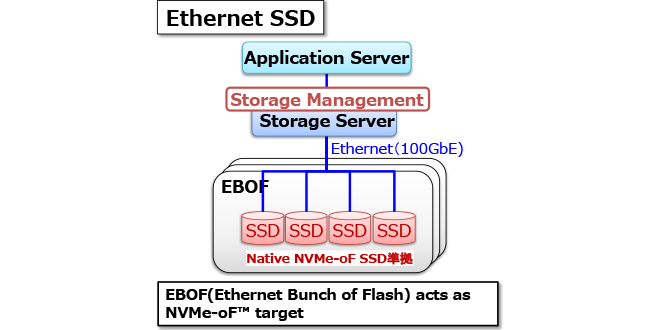

Usually networked storage is implemented on storage servers with multiple SSDs. However, now it becomes true that storage servers cannot fully utilize the high-speed performance and low latency of NVMe SSDs due to the bottleneck of computing power and limited network bandwidth. To solve this problem, Kioxia is developing SSD that connects directly to the network and enables high-speed, low-latency access (Ethernet SSD).

-

In sort benchmark contest founded by Dr. Jim Gray who was a winner of ACM A.M. Turing Award, there is a category called JouleSort to compete energy consumption in data sorting. Our sorting algorithm KioxiaSort was awarded a JouleSort world record on November 27 in 2019.

-

In order to achieve a large-capacity storage using NAND Flash memory and BiCS FLASH™ (hereinafter, referred to as NAND), many NAND packages have to be connected to a controller. We have proposed a daisy-chain configuration using bridge chips, to achieve high-speed operation and large capacity with fewer signal lines.

-

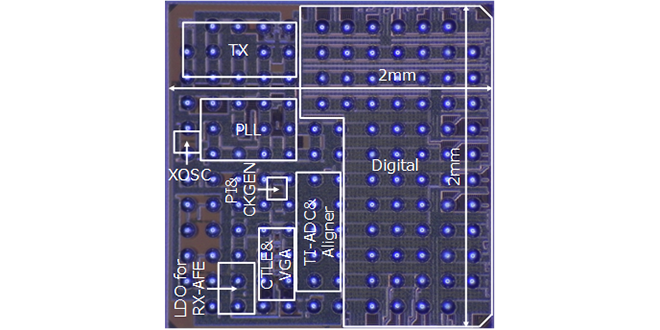

We have developed an AI accelerator for deep learning and presented it at an International conference on semiconductor circuits, A-SSCC 2018.

-

HMB technology utilizes part of the host memory (DRAM) as if it were its own, and achieves equivalent performance to an SSD with DRAM. As cooperation between the host driver and SSD is necessary, we developed HMB protocols for booting and connection, and have them incorporate PCIe® SSD interface standard, NVMe™ 1.2* with major CPU/OS vendors.

* An interface specification developed for SSDs

NVMe is a trademark of NVMe Express, Inc. PCIe is registered trademark of PCI-SIG.

R&D Organization

We aim to pursue continuous technological exploration and its social implementation to achieve an affluent and sustainable digitalized society through innovative memory technologies.

Conducts R&D on BiCS FLASH™, a type of 3D flash memory that KIOXIA was the first to develop in the world, while serving as a bridge between R&D and volume production.