Please select your location and preferred language where available.

Rethinking the erase operation of low-latency SSDs to achieve high throughput and less long latency

September 20, 2023

Flash memory requires an erase operation before writing data. The erase operation is executed in block units (several MB to tens of MB), which takes much longer to complete compared to the read/write operations that are executed in page units (4KB to 16KB). Therefore, the erase operation can be a factor causing performance degradation in SSDs, such as reduced throughput and longer latency. This is true even for low-latency flash memory-based SSDs (low-latency SSDs).

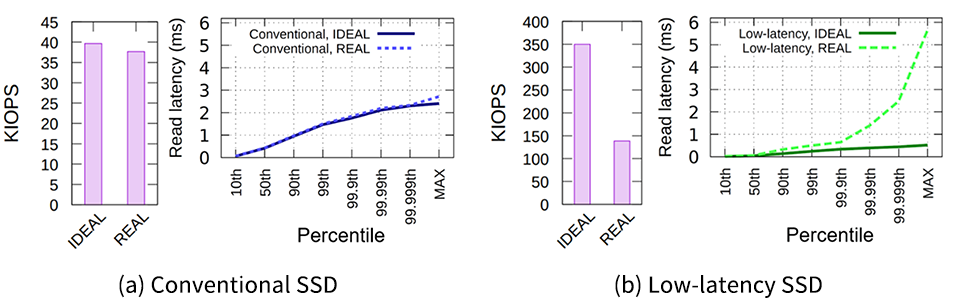

To mitigate performance degradation caused by erase operations, the erase suspension technique is widely used [1][2]. Conventional SSDs could achieve performance close to the ideal configuration (zero erase operation time) by using the erase suspension technique (Figure 1(a)). However, low-latency SSDs, even when employing the state-of-the-art erase suspension technique, cannot sufficiently hide the impacts of the erase operation, resulting in a significant drop in throughput and an increase in latency (Figure 1(b)). This is due to the erase operation in low-latency flash memory being barely accelerated compared to the read/write operations.

The difference between IDEAL (zero erase operation time)

and REAL (actual erase operation time) is the impact of erase operation.

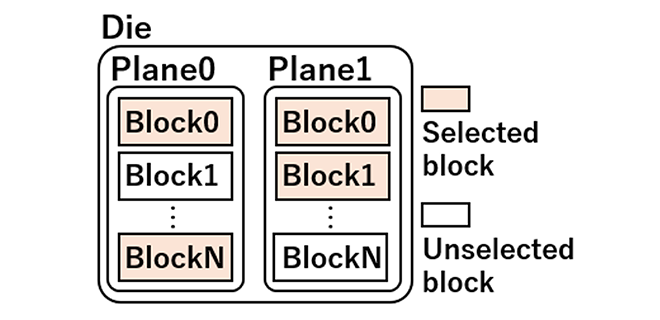

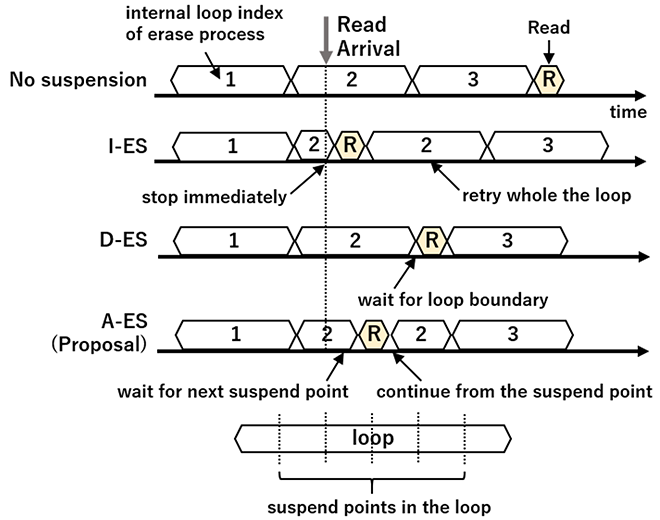

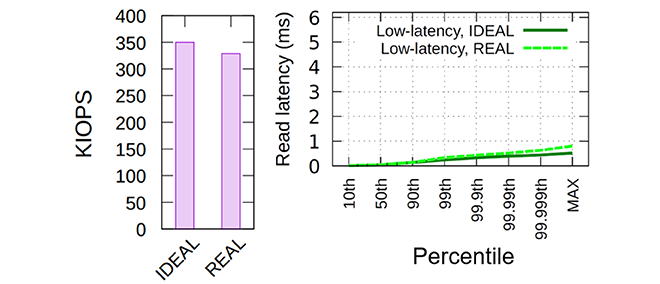

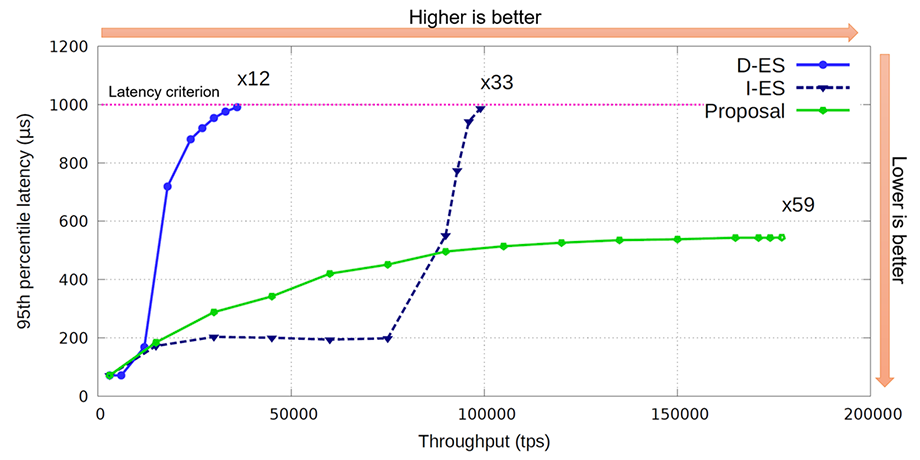

To achieve high throughput and less long latency, we proposed a boost and stop erase (BOOSTER) technique, which combines a multi-block erase technique that improves erase throughput (Figure 2) and an adaptive erase suspension (A-ES) technique that improves latency performance by setting suspend points independently from the boundary of the erase process inside the NAND flash memory (Figure 3). The BOOSTER technique reduced the burden of erase operations in low latency flash memory by increasing erase throughput and masking its overhead with independent suspend points (Figure 4). Compared to the state-of-the-art techniques, the BOOSTER technique achieved superior performance in terms of both throughput and latency in Aerospike Certification Tool evaluation [3] (Figure 5).

Fig.3: Erase suspension techniques.

(I-ES and D-ES are state-of-the-art erase suspension techniques [1].)

The proposed technique passed performance test up to 59× load, while D-ES and I-ES passed performance test up to 12× and 33× load, respectively.

This article is reconstructed from an excerpt of reference [4] presented at the 16th ACM International Conference on Systems and Storage (SYSTOR '23) in June 2023.

Reference

[1] Shine Kim, Jonghyun Bae, Hakbeom Jang, Wenjing Jin, Jeonghun Gong, Seungyeon Lee, Tae Jun Ham, and Jae W. Lee. 2019. Practical Erase Suspension for Modern Low-latency SSDs. In 2019 USENIX Annual Technical Conference (USENIX ATC 19). USENIX Association, Renton, WA, 813–820.

[2] Guanying Wu and Xubin He. 2012. Reducing SSD Read Latency via NAND Flash Program and Erase Suspension. In 10th USENIX Conference on File and Storage Technologies (FAST 12). USENIX Association, San Jose, CA.

[3] Aerospike Certification Tool.

https://github.com/aerospike/act

[4] Takumi Fujimori and Shuou Nomura. 2023. BOOSTER: Rethinking the erase operation of low-latency SSDs to achieve high throughput and less long latency. In Proceedings of the 16th ACM International Conference on Systems and Storage (SYSTOR '23). Association for Computing Machinery, New York, NY, USA, 94–104. https://doi.org/10.1145/3579370.3594774