Please select your location and preferred language where available.

近年の機械学習およびAI(人工知能)の急速な進歩により、大容量かつ高速で動作可能なメモリへの需要が高まっています。大容量化のためにはメモリセルの微細化や積層化、高速動作のためには駆動電流の向上が必要になります。

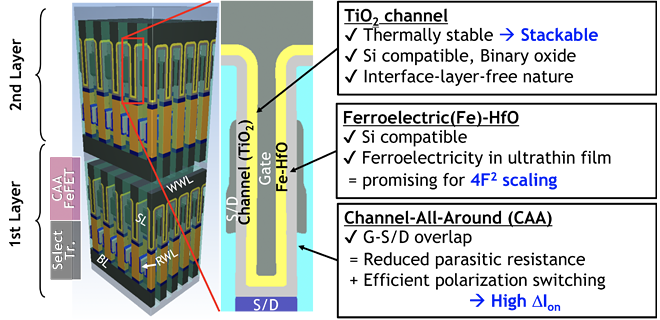

図1は、今回提案した大容量と高速動作の両立を可能にするメモリのコンセプトです。鍵となるのは、TiO2チャネルとHfO強誘電体ゲート絶縁膜で構成される強誘電体トランジスタ(Ferroelectric Field Effect Transistor, FeFET)です。これまでに私たちは、TiO2 FeFETが高速・低消費電力・高耐久の有望なメモリ素子であることを示してきました[1]。

今回のコンセプトでは、縦型のChannel-All-Around (CAA) 構造を採用しているところがポイントとなります。縦型であることによりセルサイズの微細化、CAA構造であることにより駆動電流の向上が期待されます。さらにTiO2は熱的に安定な酸化物半導体と考えられているため、メモリセルアレイの積層による大容量化を図ることができます[2]。

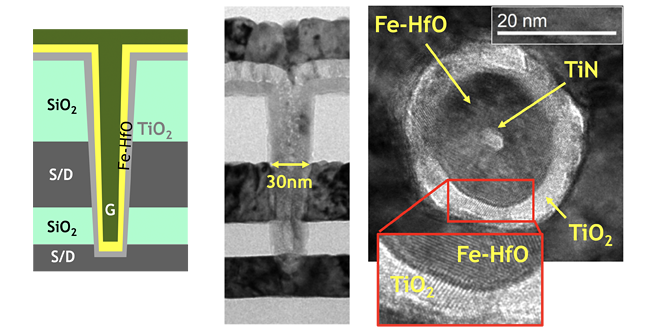

図2は、実際に300mmウェハ上に試作したCAA型TiO2 FeFETの断面TEM像と平面TEM像です。30nm径の微細なホール内に、TiO2チャネル、強誘電体HfO (Fe-HfO)、TiN電極がしっかり穴底まで埋め込まれている様子が見て取れます。また、平面TEM像を拡大するとTiO2とFe-HfO膜中に干渉縞が見られ、それぞれの膜が結晶化していることが示唆されます。このことから、良好な耐熱性と強誘電性の発現を期待することができます。

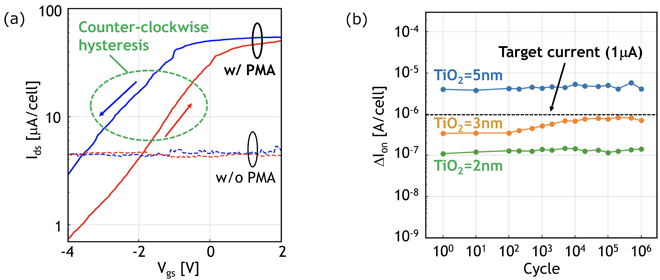

図3は、30nm径のCAA FeFETの(a) Id-Vg特性と(b) Endurance特性を示しています。Id-Vg特性において、PMA (Post Metallization Anneal) を実施することにより反時計回りのヒステリシスが観測され、強誘電体の分極反転に起因するメモリ動作を確認することができました。また、Endurance特性において、106cycle以上の安定した動作を確認することができ、特にTiO2膜厚が5nmの素子では目標電流(1μA)と安定動作を両立することができました。

これらの良好な特性を、30nm径という微細なメモリセル内で実現できたところがポイントで、将来向けの大容量かつ高速動作が可能なメモリへの適用が期待できるメモリデバイスであると考えています。

本技術は、2024年6月に米国ハワイにおいて開催された国際学会IEEE Symposium on VLSI Technology and Circuits 2024において発表を行いました。

文献

[1] 先端技術トピックス「高性能・低消費電力AI応用に向けたTiO2チャネル強誘電体FETの動作実証」, 2023年5月31日

[2] S. Kabuyanagi et. al., “A Vertical Channel-All-Around FeFET with Thermally Stable Oxide Semiconductor Achieving High ΔIon > 2μA/cell for 3D Stackable 4F2 High Speed Memory”, 2024 IEEE Symposium on VLSI Technology and Circuits, T8-2.