Please select your location and preferred language where available.

目覚ましい発展を遂げている機械学習やAI(人工知能)応用に向け、高性能・低消費電力メモリチップの要求が加速しています。トランジスタのゲート絶縁膜に強誘電体二酸化ハフニウム(HfO2)を用いた強誘電体FET(Ferroelectric Field Effect Transistor, FeFET)は高速・低電圧動作が可能であること、CMOSプロセスとの親和性が高いことからその有力な候補として注目されています[1]。

FeFETのチャネル材料にはSiが多く用いられてきました。このSi-FeFETの課題として、チャネル/強誘電体膜界面に低誘電率界面層が形成されることが知られています。特に、書き込み/消去を繰り返すことでこの界面層が劣化することにより、書き換え耐性(エンデュランス)が制限されることは、Si-FeFETの応用を妨げる要因のひとつとなっています[2]。

近年、この課題を解決するため酸化物半導体(Oxide Semiconductor, OS)をチャネルに用いたFeFET(OS-FeFET)が提案されています。OS-FeFETはチャネルが酸化物であることから、従来のSi-FeFETで課題となる低誘電率界面層が形成されず、エンデュランス特性の大幅な改善が期待されます。これまで、OS-FeFETのチャネル材料としては酸化インジウムを含む化合物が多く報告されてきました。しかし、酸化インジウムを含む材料をチャネルに用いたOS-FeFETはFeFETの利点であるCMOSプロセスとの親和性や、プロセス耐熱性を低下させるため、これらの課題を解決する新たなチャネル材料が求められています。

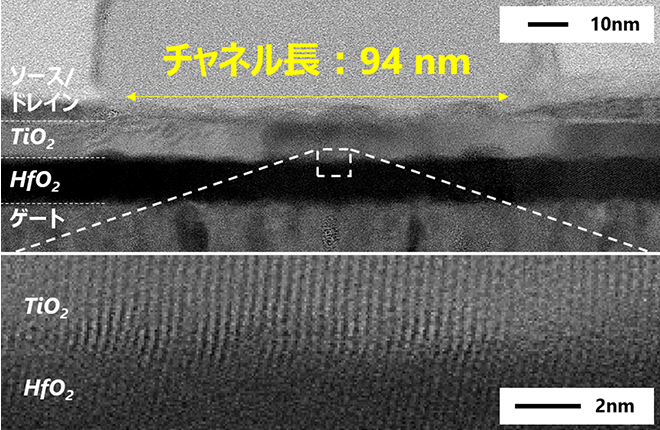

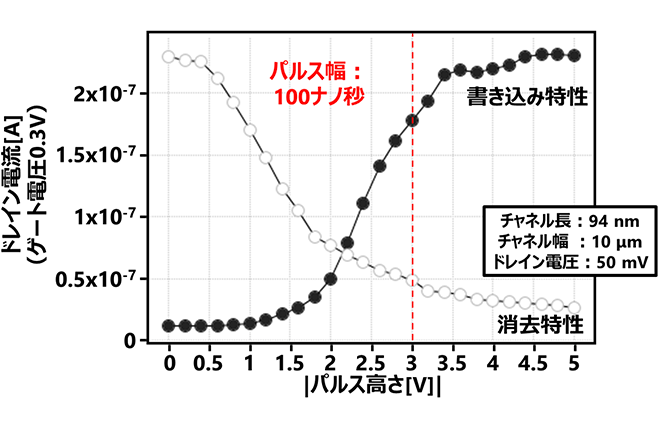

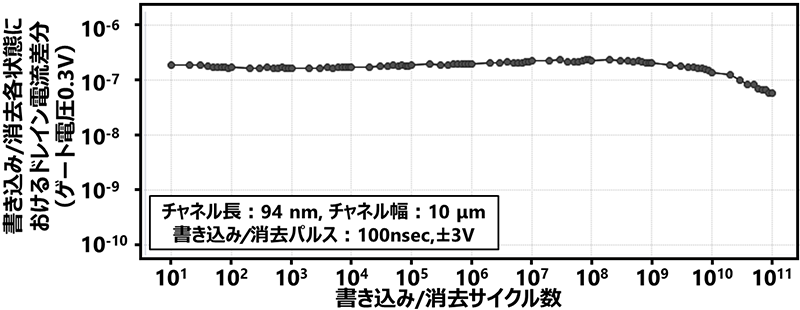

そこで、私たちは二酸化チタン(TiO2)に着目しました。二酸化チタンはCMOSプロセスでよく用いられる材料でありながら、高い電界効果移動度、熱安定性をもつ酸化物半導体チャネル材料として有望視されています。本研究では、世界で初めてチャネル長を100nm以下まで微細化したTiO2-FeFETを試作し(図1)、高速・低電圧条件(100ナノ秒/3V)での書き込み/消去動作を実証しました(図2)。加えて、今回動作実証に成功したTiO2-FeFETは、1011サイクル以上の高いエンデュランスを達成しました(図3)。これらの成果は、高速・低消費電力・高耐久メモリ素子としてTiO2-FeFETが有望であることを示しており、機械学習やAI向け高性能メモリチップの実現に向けて大きな進歩であると考えられます。

本稿は、2023年3月に開催された7th IEEE Electron Devices Technology and Manufacturing (EDTM) Conference 2023で発表され、Best Contributed Paper Awardを受賞した文献[3]から図面等一部抜粋&再構成したものです。

文献

[1] 先端技術トピックス「低消費電力高集積AI応用に向けたHfO2系強誘電メモリ」, 2021年2月25日

[2] 先端技術トピックス「高速荷電中心解析によるチャージトラップのダイナミクス把握に基づくHfO2-FeFETサイクル劣化機構解明」, 2022年2月24日

[3] Taro Shiokawa, Reika Ichihara, Takamasa Hamai, Kiwamu Sakuma, Kota Takahashi, Kazuhiro Matsuo and Masumi Saitoh, “High-Endurance (>1011cycles) and Thermally-Stable Sub-100nm TiO2 Channel FeFET for Low-Power Memory Centric 3D-LSI Applications,” 7th IEEE Electron Devices Technology and Manufacturing (EDTM) Conference, pp.334-336 (2023).