Please select your location and preferred language where available.

電荷蓄積メモリは、ゲート絶縁膜中のトラップ(欠陥準位)に捕獲された電荷の極性や量に応じてトランジスタの閾値電圧が変調することを利用した不揮発メモリです。信頼性の観点から、長期的な閾値電圧の変化はもちろん、短期的な閾値変調についても理解することが非常に重要です。しかし、1秒以下の短時間領域における電荷トラップ特性はこれまでよく分かっていませんでした。

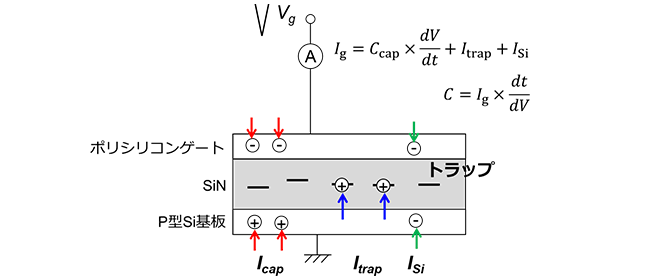

そこで、私たちは最短で10µsオーダーを含む広い時間領域における電荷トラップ特性を直接把握する手法を構築しました。この手法では、MIS(Metal Insulator Semiconductor)キャパシタへの充放電に加えて、トラップへの電荷捕獲/放出を直接かつ高速に測定します(図1)。

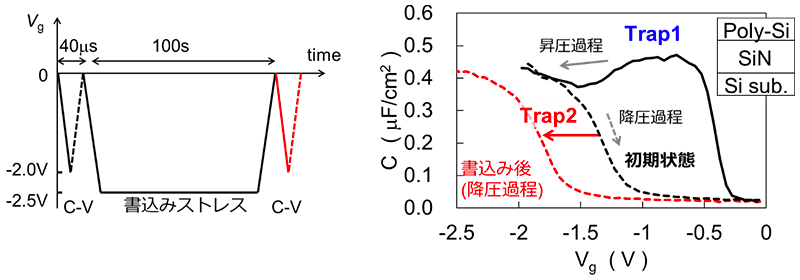

この手法を、SiN膜をゲート絶縁膜とするMISキャパシタに適用したところ、SiNには2種類の正孔トラップがあることが分かりました。図2に今回構築した手法で計測した容量-電圧特性を示します。昇圧過程(実線)でなだらかなピークが確認されますが、これは-0.7V程度の低い電圧でトラップへの正孔捕獲が生じたことを直接捉えたものです。昇圧過程にかかる時間は約10µsのため、このホール捕獲は極めて短時間で起こるものと考えられ、今回の手法により初めて把握されました(Trap1)。より高い電圧(-2.5V)を100s加えると、CV特性が負方向にシフトします(図2の黒破線から赤破線にシフト)。これは、追加の正孔捕獲が生じたことを示しており、Trap1に比べてより高い電圧下で長い時間をかけて正孔を捕獲するトラップ(Trap2)の存在が明らかになりました。

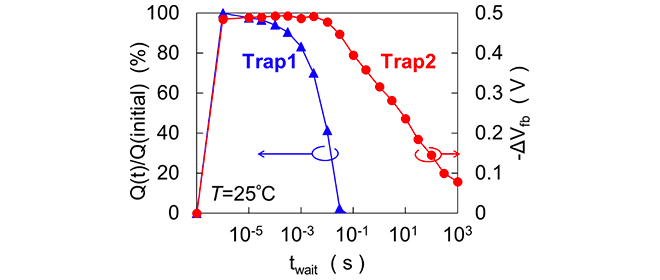

次に、それぞれのトラップのホール放出過程を調べました(図3)。Trap1からのホール放出は10µs以降に顕在化し、30ms以内にほぼ完了します。一方、Trap2から全てのホールが放出するには1,000s以上の時間がかかります。Trap1はTrap2に比べて、ホールの捕獲だけでなく放出も速い、時定数の短いトラップであることがわかりました。

この研究で構築した測定手法と、それにより得られた短時間領域を含むSiN膜中トラップの包括的な描像は、電荷蓄積メモリの特性向上に寄与できると考えます。

この成果は2023年3月に開催された国際学会IRPS(International Reliability Physics Symposium)において発表されました[1]。

文献

[1] H. Seki, et al., IRPS2023, 3A4