Please select your location and preferred language where available.

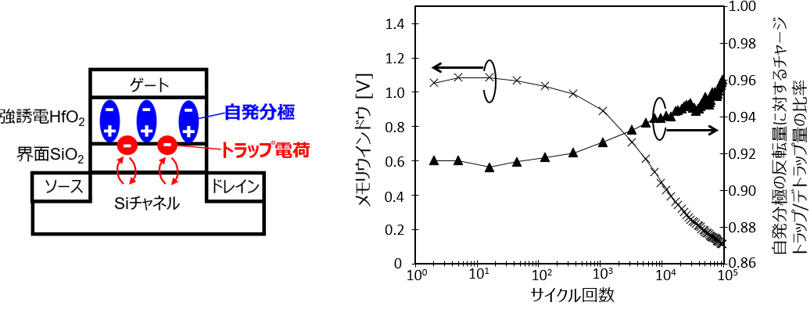

近年、MIS*1トランジスタのゲート絶縁膜に強誘電体を用いたFeFET(Ferroelectric FET)が次世代メモリの有力候補として注目されています。FeFETは強誘電膜の自発分極反転に伴うVth(閾値電圧)の変調を利用したメモリで、なかでも強誘電性HfO2を用いたFeFETは、低電圧・高速動作が可能であることに加え、CMOSプロセスとの整合性が良いというメリットを有します。

FeFETでは、自発分極の反転のみならず、その効果を妨げる極性の電荷トラップ/デトラップが生じます。この電荷トラップ/デトラップはその量が自発分極の反転量の約90%にも及ぶ莫大なものであり、FeFETの課題の1つであるサイクル劣化(書込/消去の繰り返しに伴う劣化)の原因であることが分かっています[1,2]。具体的には、サイクルと共に自発分極の反転量に対する電荷トラップ/デトラップ量の比率が増え、結果としてメモリウインドウ(分極反転に伴うVth変化量)が減少します(図1)[1,2]。しかし、劣化に関わるトラップ電荷の種類(電子かホールか)や、電荷トラップ/デトラップ比の比率が増える機構は明らかではありませんでした。

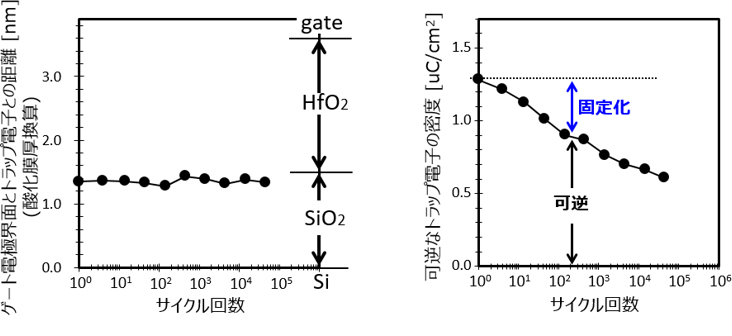

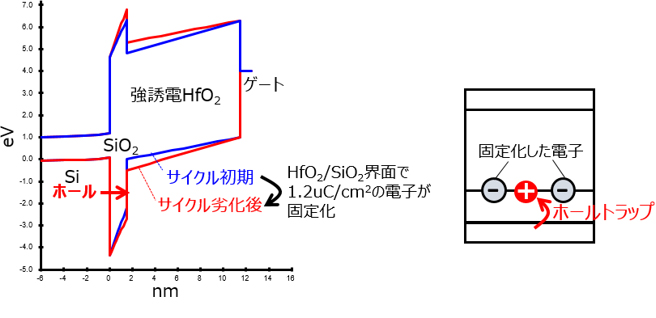

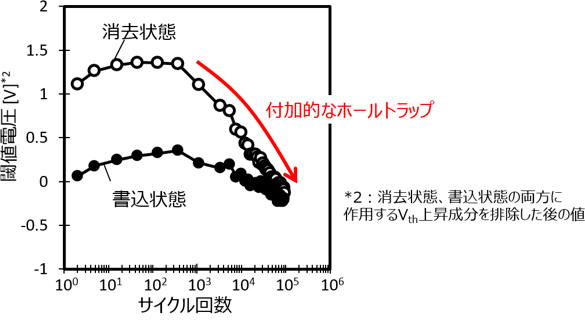

今回私達は、電荷トラップ/デトラップに伴うゲートを介した電荷の出入りとドレイン電流を同時に計測する手法を用い、HfO2-FeFETにおける様々な種類の電荷トラップ/デトラップの振る舞いを定量的に抽出しました。その結果、書込動作の際にHfO2とその下のSiO2の間の界面にトラップされた電子の一部がサイクル過程で固定化すること(図2)、固定化した電子がSiO2の電界を変調して消去動作の際に付加的なホールトラップを誘発すること(図3)が分かりました。このホールトラップは、書き込みと共に放出する可逆な成分であるため、メモリウインドウの減少に直結しています(図4)。電子トラップの抑制だけでなく、その固定化を防ぐことが、サイクル耐性向上の鍵であることが明らかになり、FeFETの信頼性向上に向けた重要な知見が得られました。

本成果は2021年12月に開催された国際学会IEDM(International Electron Devices Meeting)において発表されました[3]。

本稿は、文献[3]@2021 IEEEから図面等一部を抜粋&再構成したものです。

- Metal Insulator Semiconductor

文献

[1] R. Ichihara et al., VLSI2020, TF1.2.

[2] M. Saitoh et al., IEDM2020, 375.

[3] R. Ichihara et al., IEDM2021, 131.