Please select your location and preferred language where available.

近年、半導体デバイスの構造は複雑化しており、幾つもの加工プロセスを経て製品が完成するまでに数ヶ月を要するものもあります。完成品は厳格な電気テストが行われ、合格品が出荷されます。一方、テストで不合格の製品はただちに解析調査が行われ対策を進めますが、不良原因がプロセス装置に起因する場合、異常プロセス装置を特定するまでの間は不良品を作り続けることになります。そのため我々はプロセス途中にダストやパターン異常といった加工プロセス欠陥を監視する製造ライン(インライン)モニター網を張り巡らせています。検出した欠陥は高解像の走査型電子顕微鏡(SEM*1)を用いてダストやパターン異常(断線やショート)のように欠陥種毎に分類され、欠陥種から異常プロセス装置を特定し改善が短期間で行われます。現在では分類作業は深層学習(Deep Learning)にて自動化されており、短時間で製造ラインを健全化するシステムが構築されています。また、インラインの欠陥データ(種類、座標、大きさ)は製品完成時の電気テスト合格率(不良品リスク)の予測にも活用されています。しかしながら、予測精度が56%と低いインライン検査工程も存在しており改善が求められていました。

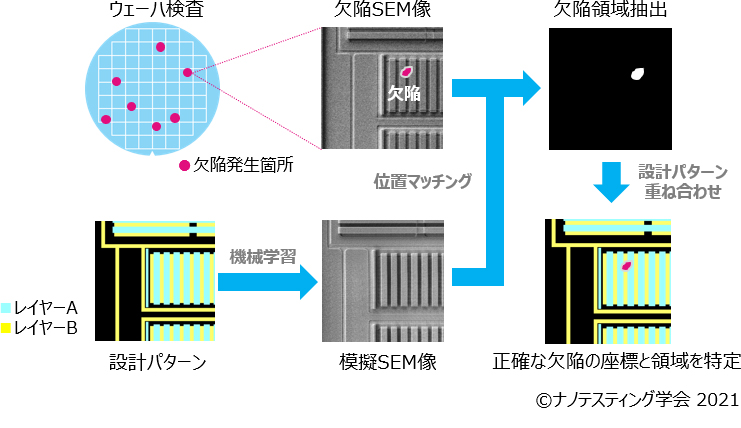

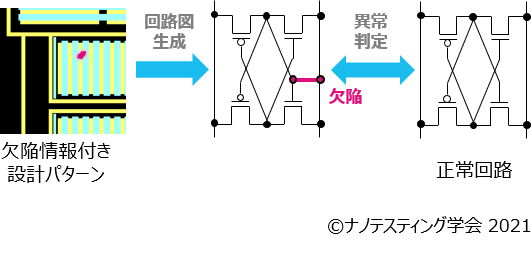

今回我々はインライン欠陥データと設計レイアウトデータのデジタライゼーションに取り組みました。まず、図1に示すように、機械学習を用いて設計レイアウト(CAD*2)から正常パターンの模擬SEM像を生成し、欠陥のSEM像と比較することで高精度な欠陥情報(座標と領域)を抽出することが可能になりました[1]。次に、この欠陥情報と設計レイアウトから設計検証ツールのひとつであるLVS*3を用いて電気回路図を作成し、電気テストの合否を高精度に予測します(図2)。提案手法により、前述の合格率予測精度を73%に改善することに成功しました。今後も最新の欠陥検査装置技術やデジタル処理技術をインテグレートし、スマート工場の高度化を推進してまいります。

この成果は、半導体パターニング技術に関する国際会議「SPIE (The International Society for Optical Engineering) Advanced Lithography 2021」で発表しました[2][3]。

- Scanning Electron Microscope

- Computer Aided Design

- Layout vs Schematic

文献

[1] T. Ohashi, Y. Konno, A. Nakajima, C. Ida, A. Hamaguchi, “A study of lithography process prediction using GAN”, NANO Testing Symposium 2019

[2] J. Okude, C. Ida, K. Nojima, A. Hamaguchi, “In-line schematic failure analysis technique by defect SEM images”, Proceedings of SPIE - The International Society for Optical Engineering, 11611, 116110M

[3] J. Okude, C. Ida, K. Nojima, A. Hamaguchi, “In-line schematic failure analysis technique by fewer frame defect SEM images”, NANO Testing Symposium 2021