Please select your location and preferred language where available.

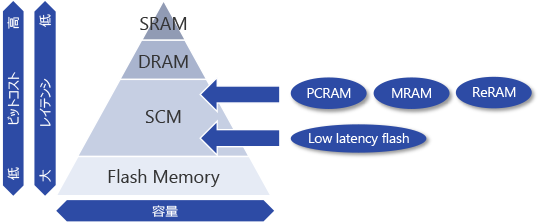

5Gの伸長などにあわせて、生成されるデータが爆発的に増えていき、生成されたデータは機械学習やAIといった様々なアプリケーションでCPUが処理するためにデータベース化されストレージに保存されています。現在のコンピューティングシステムでは、データを処理するためにデータが保存されているストレージ空間からCPUがデータを処理するためのメモリ空間へのデータの転送やデータの入れ替えが発生します。しかし、メモリ空間のデバイスであるDRAMとストレージ空間のデバイスである フラッシュメモリを用いた SSDの間に大きな性能ギャップがあり、データの処理効率が良いとは言えません。そのため、データの入れ替えを少なくするために、主記憶容量の拡張と、データの転送を高速にするためのストレージ容量の低レイテンシ化が求められています(図1)。

- メモリ空間を拡張すれば、CPUが一度に扱えるデータが増えるため、システムの処理効率が向上。

- ストレージを低レイテンシ化、大容量化すれば、DRAMへのデータ転送効率が向上して、システムの処理効率が向上。

そのDRAMとフラッシュメモリの間の性能・容量ギャップを埋めるために、SCM(ストレージクラスメモリ)と呼ばれる階層があり、様々なデバイス候補(図2)を各社が開発しています。当社もこのSCM領域をターゲットにした低レイテンシフラッシュメモリの一つである XL-FLASH™を開発しています。XL-FLASH™はリードアクセスにかかる時間(リードレイテンシ)が 5μsと一般的なフラッシュメモリと比較して、非常に高速なフラッシュメモリとなっています(表1)。

表1:XL-FLASH™と従来のフラッシュメモリの比較

|

XL-FLASH™[1] |

Conventional[2] |

|

|---|---|---|

|

リードレイテンシ |

<5μs |

58μs |

|

容量 |

128Gbits |

512Gbits |

|

ページサイズ |

4KB |

16KB |

今回我々はDRAMと比較して、低ビットコスト(コスト当たりの容量が大きい)・大容量であるXL-FLASH™を用いてDRAMの代替を狙った実証をデータベースをモチーフに行いました。XL-FLASH™をDRAM代替用途で使用するためには、1) 効率的なデータ転送インタフェース と、2) データ配置最適化 がキーポイントとなります。1)に対しては、現在、高性能SSDで一般的に用いられるNVM Express™*1プロトコルのコマンドオーバーヘッドを減らしたインタフェースを開発し、2)に対しては、データベースでアクセス頻度の低いデータをXL-FLASH™に配置するデータベースを試作しました。

これらの評価のためXL-FLASH™デモドライブを作製し(図3)、実サーバーを用いた評価により、DRAMを用いたデータベースとXL-FLASH™を用いたデータベースが、リードアクセスが主体の状況において同等の性能を出していることを示しました(図4)。これにより、データ爆発時代に向けて、XL-FLASH™がデータベース用途においてコンピューティングシステムの課題を解決する可能性があることを示しました。

|

ホストインタフェース |

PCIe®*2Gen3, 4lanes |

|---|---|

|

フラッシュメモリパッケージ数 |

XL-FLASH™ |

|

ドライブ容量 |

1TB |

|

256Byteランダムリード |

8M IOPS*3 |

|

ドライブリードレイテンシ |

10μs |

本技術は2020年5月に開催された国際学会「International Memory Workshop」においてInvited Keynoteとして発表を行いました[3]。

- NVM ExpressはNVM Express Inc.の商標です

- PCIeはPCI-SIGの登録商標です

その他記載されている社名・商品名・サービス名などは、それぞれ各社が商標として使用している場合があります。 - IOPS: Input Output Per Second

[1] Kioxia press release, August 5, 2019

http://americas.kioxia.com/en-us/business/news/2019/memory-20190805-1.html

[2] H. Maejima et al., “A 512Gb 3b/Cell 3D Flash Memory on a 96-Word-Line-Layer Technology”, Digest of Technical Papers - IEEE International Solid-State Circuits Conference, pp. 336-338

[3] T. Shiozawa, K. Hiwada, H. Kajihara, and T. Endo, “Emerging Usage and Evaluation of Low Latency FLASH,” IEEE International Memory Workshop, IMW 2020, pp. 8-11

本稿は、文献[3]@2020 IEEEから図面等一部抜粋&再構成したものです。