Please select your location and preferred language where available.

AI(人工知能)、Big data処理など、新たな応用に対する需要が急速に増大し、これまでのメモリ階層構造に変革が求められています。特に、高性能かつ低コストなStorage-Class Memory (SCM) と呼ばれる新しい階層を設けることにより、効率的なコンピューティングを実現できると考えられています。

次世代不揮発メモリの有力候補の一つに、メモリ素子としてp-MTJ(垂直磁化-磁気トンネル接合)を用いたSTT-MRAM(スピン注入磁化反転型磁気メモリ)があります。STT-MRAMは、既に混載応用や単体メモリとして市場に流通しています。しかし、トランジスタを選択素子に用いた構造は大容量化に課題があり、2016年に韓国SK hynix社と共同で開発した4 GbitのSTT-MRAMが今でも最大容量となっています[1]。

MTJは高速動作や信頼性の観点で実証された技術ではありますが、STT-MRAMの大容量化にはこれまでいくつかの課題がありました。それは主に、選択トランジスタの書込み電流不足、微細かつ狭ピッチなMTJの加工、信頼性の高いセル動作、の3つになります。我々は、トランジスタに代えて2端子セレクタ(Selector)素子を使うことにより、十分な書込み電流を確保し、基本的なセル動作を2022年に実証しました[2]。

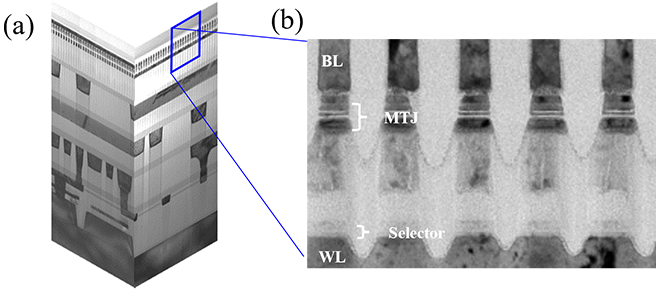

今回、IEDM2024において、残り二つの課題に対処する技術を示すことが出来ました[3]。図1は、韓国SK hynix社と共同で作製した64GbitクロスポイントMRAMの(a)鳥瞰TEM像、(b)断面TEM像です。微細かつ狭ピッチなMTJの加工を実現するには、MTJ材料と加工プロセスを共に最適化することが必要です。我々は、MTJ直径20nm、ハーフピッチ20.5nmで、特性劣化を防ぎながらMTJや配線間の電気的なショートを防ぐことに成功しました。これは、MRAMとしては世界最小のセル面積0.001681μm2に相当します。

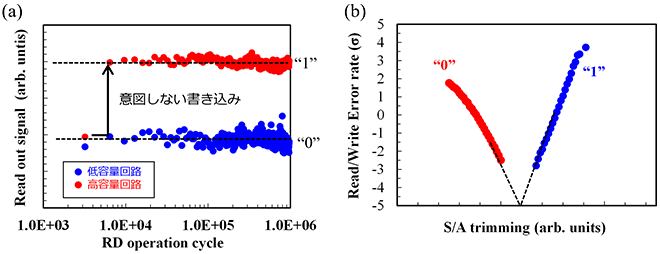

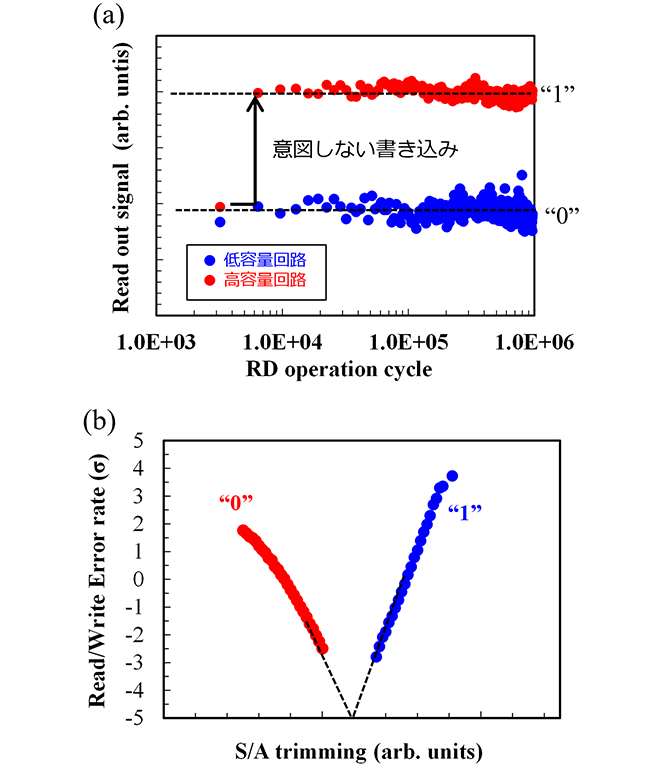

従来の読出し方法では、特に微細なMTJで、セレクタがオンする時に意図しない書込み動作が発生し、セル動作の信頼性が損なわれます。我々は、セレクタの過渡特性を利用した読出し方法と低容量な回路方式を組み合わせて、この問題を解決しました。図2(a)は、低抵抗状態“0”に初期化したMTJに対して、繰り返し読出し試験をした結果です。高容量回路(赤)を適用した場合、すぐに高抵抗状態“1”に書き換わってしまいます。一方、低容量回路(青)では、少なくとも100万回の読出し動作を繰り返した場合でもMTJの状態が変化しないことを表しています。

図2(b)は、典型的な1ビットに対して、読出しと書込みを繰り返し行い、セル動作の不良確率を測定したものです。最適な回路設定を行えば、不良確率は-5σ(2.87e-07)程度となり、信頼性の高いセル動作を実現できることを示しています。

これらの結果は、大容量MRAM実現の道を切り開くものであり、高性能かつ低コストなSCM応用のポテンシャルを示しています。

本成果は2024年12月に開催されたIEEE IEDM 2024において発表されました。

文献

[1] S.-W. Chung et al., “4Gbit density STT-MRAM using perpendicular MTJ realized with compact cell structure”, IEDM Tech. Digest, pp.659-662, 2016

[2] S.M. Seo et al., “First demonstration of full integration and characterization of 4F2 1S1M cells with 45 nm of pitch and 20 nm of MTJ size”, IEDM Tech. Digest, pp.218-221, 2022

[3] Hisanori Aikawa et al., “Reliable memory operation with low read disturb rate in the world smallest 1Selector-1MTJ cell for 64 Gb cross-point MRAM”,2024 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 10-1