Please select your location and preferred language where available.

将来世代3次元フラッシュメモリ向け新規水平チャネルフラッシュメモリ(Horizontal channel flash)の開発

2025年3月5日

3次元フラッシュメモリは、セル密度を高める高積層化によってコスト低減を実現してきました。しかし、コスト低減の限界や速度性能に関わるセル電流の低下が、高積層化時の課題として近年指摘されてきています[1]。そこで我々は、高積層化してもセル電流が劣化せず、コスト低減可能性のある新規水平チャネルフラッシュメモリの提案・動作実証を行いました[2]。

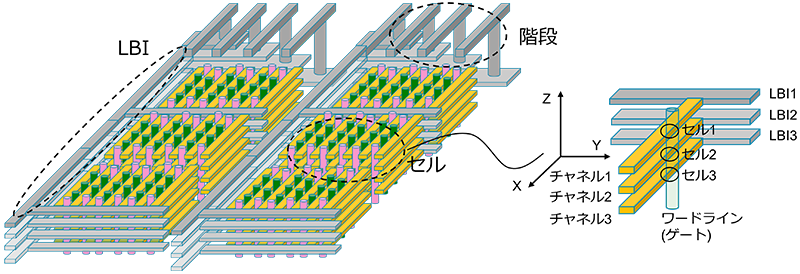

水平チャネルフラッシュメモリは図1に示すように、セル部と階段部、およびそれらをつなぐLBI (Local Block Interconnect) と呼ばれる構造で構成されています。セル部はデータを保存する領域、階段はセルに保存されたデータを外部へ電気的な信号として送る接続領域、LBIはそれらを電気的につなぐための金属配線です。従来の3次元フラッシュメモリと異なり、チャネル方向が基板垂直方向(Z軸方向)ではなく基板水平方向(XY平面)に形成されているのが特徴で、チャネル方向は積層数とは関係が無いため、高積層化してもセル電流低下が起きない利点があります。またセル部では、チャネル(XY平面)とワードライン(Z軸方向)の交点にデータを保存するセルが形成されるため、3次元的にセルが高密度に形成される構造となっています。

セル部と階段部、それらをつなぐ金属配線(LBI)で構成される ©2024 IEEE[2]

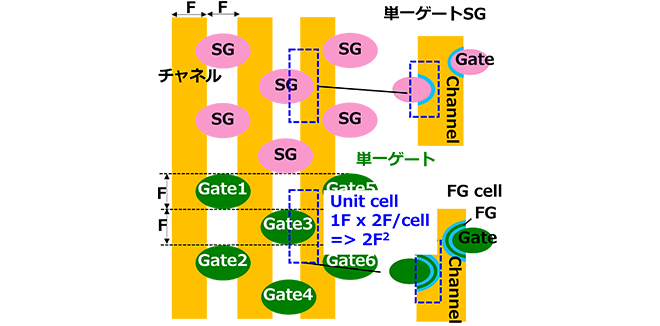

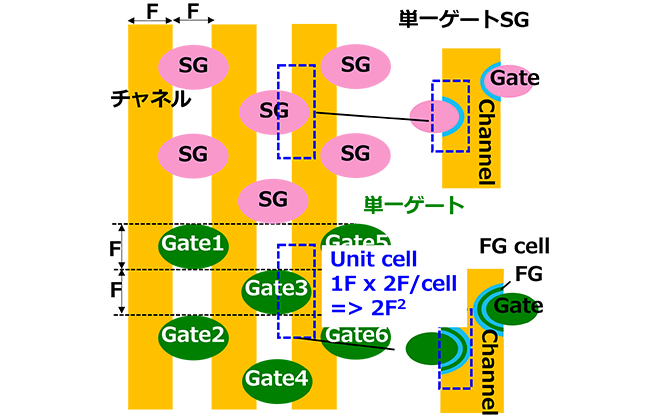

図2は、図1の中のセル部のみの模式図を示しています。一つのチャネルに対して左右両側に選択ゲート(Select Gate (SG))、浮遊ゲート(Floating Gate (FG))セルが形成されています。ここで選択ゲートはどのチャネルかを選択する電気的なスイッチ、浮遊ゲートセルはデータを保存する構造です。チャネル両側に浮遊ゲートセルが形成されてセル密度が高くなるため、従来の3次元フラッシュメモリ構造よりコスト低減の可能性があります。

上下にのびるチャネル(橙)の両側にセルが形成される ©2024 IEEE[2]

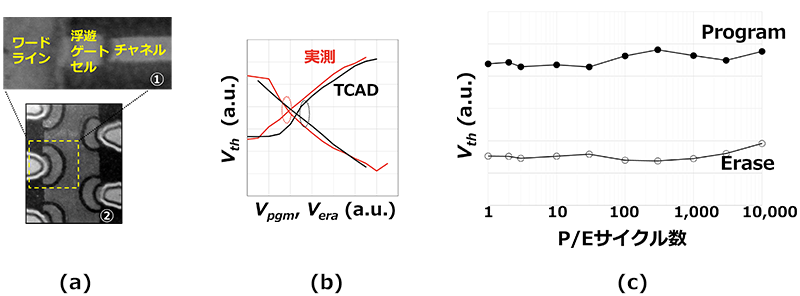

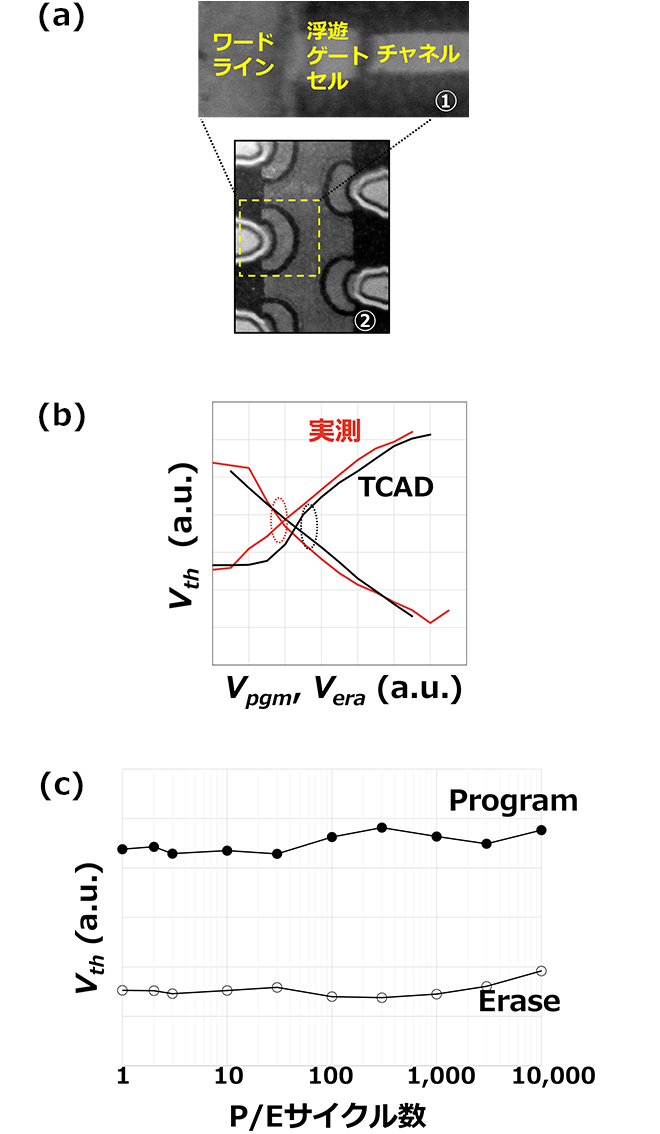

このような水平チャネルフラッシュメモリのセル構造を試作し、Program/Erase動作特性を評価しました。図3(a)に、試作したセル構造の断面TEM (Transmission Electron Microscope) 像を示します。ワードラインとチャネルの間に浮遊ゲートセルが形成されていることがわかります。

このときのセルのProgram/Erase特性について、実測とTCAD (Technology Computer Aided Design) シミュレーション予測との比較を図3(b)に示します。シミュレーションの予測どおり、Program/Eraseパルスによって閾値Vthが変化することを確認しました。

さらに図3(c)に示すように、1万回のProgram/Erase動作後も閾値の変動が無く、セルが安定的に動作していることが実証されました。

以上のように、現在の3次元フラッシュメモリの課題へ対策を行い、コスト低減の可能性がある水平チャネルセル構造の動作検証を我々は世界に先駆けて行いました。今後もセルの基礎的な特性の評価を進め、実現性を検証していきます。

本成果は2024年12月に開催されたIEEE IEDM 2024 (IEEE International Electron Devices Meeting 2024) において発表されました。

文献

[1] R. Katsumata, “Overview in three-dimensionally arrayed flash memory technology”, in Short Course. 2019 Symposium on VLSI Technology and Circuits

[2] M. Oda et al., “Superior Scalability of Advanced Horizontal Channel Flash for Future Generations of 3D Flash Memory”, in Proc. 2024 IEEE International Electron Devices Meeting (IEDM)