Please select your location and preferred language where available.

3次元フラッシュメモリのスケーラビリティと高信頼性を可能にするフッ素フリー ワードライン モリブデンプロセス

2024年9月24日

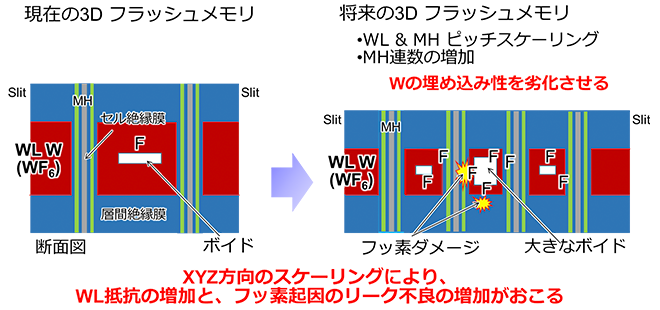

3次元フラッシュメモリで高ビット密度と低コストの両方を達成するには、積層ワードライン (WL) の数を増やすと同時に、水平方向(XY方向)と垂直方向(Z方向)にスケーリングすることが不可欠です。しかしながら、Z方向のスケーリング(WLピッチスケーリング)はWL抵抗の増加を生み、WL RCの遅延を生みます。さらに、XY方向のスケーリング(MH PitchスケーリングとMH連数増加)とZ方向のスケーリングは、共にタングステン(W)の埋め込み性を劣化させます。Wの埋め込み性が劣化すると、プリカーサーWF6起因の残留フッ素を多く含むボイドが大きくなります。このボイドに残留したフッ素は、セル絶縁膜や層間絶縁膜のエッチングを行い、リーク不良を引き起こします[1][2][3](図1)。これらの性能と信頼性の劣化は、3次元フラッシュメモリにとって最も重大なスケーリング限界要因の一つです。

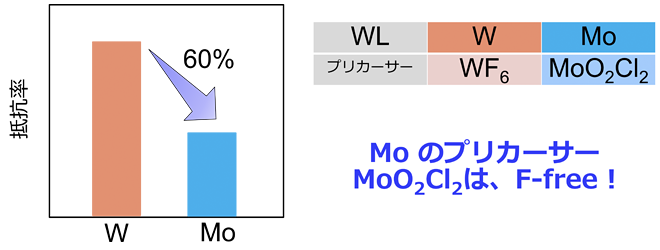

モリブデン(Mo)は、Wで起こるスケーリング限界を克服するのに適した代替材料です。まず、物理的特性として、MoはWよりも抵抗率が低く、さらに、MoのプリカーサーであるMoO2Cl2は、WのプリカーサーであるWF6と異なり、フッ素を含まないため、フッ素ダメージの懸念がありません(図2)。本稿では、最先端のフッ素フリーWL Moプロセスを採用した3次元フラッシュメモリにおいて、WL Wプロセスに対する優位性を紹介します[4]。

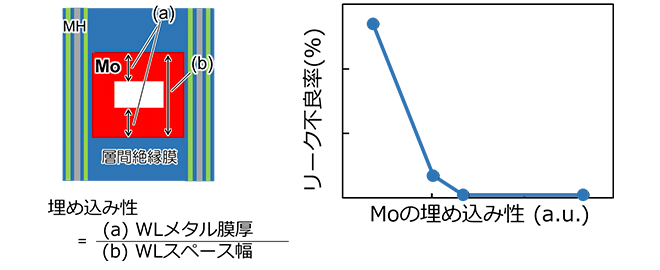

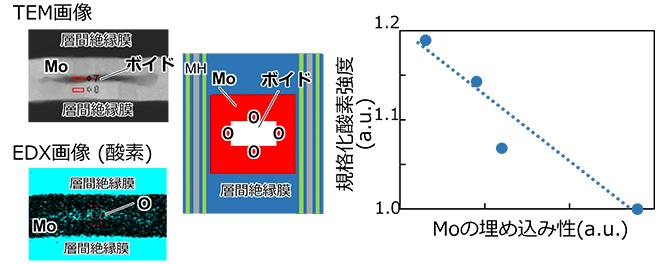

我々は、WL Moプロセスにおいても、WL Wプロセス同様に埋め込み性が重要であることを実証しました。図3は、埋め込み性とリーク不良率の関係を示した図です。埋め込み性が高くなると、リーク不良率が低減していることがわかります。 図4に埋め込み性と、飛行時間型二次イオン質量分析法(TOF-SIMS)で分析したWL Mo膜中の酸素強度の関係を示します。埋め込み性が高くなると、酸素強度が下がることがわかります。図4の左側で示した透過電子顕微鏡を用いたエネルギー分散型X線分光法(TEM-EDX)画像から、WL Mo膜中酸素は、WL Mo中のボイドに溜まっていることもわかります。これらの結果から、WL Moの埋め込み性が悪くなった際にリーク不良率が増加するモデルを構築しました。埋め込み性が悪くなると、プリカーサーMoO2Cl2起因の残留酸素を多く含むボイドが大きくなります。このボイドに残留した酸素原子が、セル絶縁膜や層間絶縁膜に拡散した際に、絶縁膜中に導電準位を形成し、リーク不良を引き起こしていると考えられます。そのため、リーク不良を低減するためには、WL Moプロセスにおいて、埋め込み性を良くすることが重要になります。

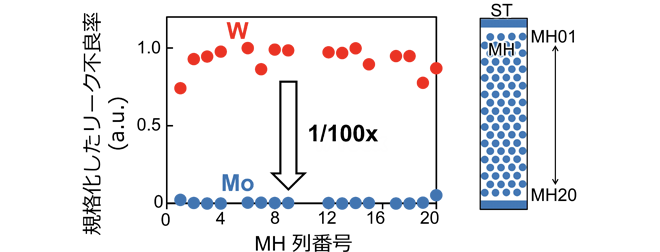

図5で、埋め込み性を改善したWL Moと、WL Wのリーク不良率の比較を示します。WL Moは、WL Wに対して100分の1のリーク不良率になっていることが確認できます。フッ素フリーのWL Moプロセスは、WL Wプロセスで問題となるフッ素ダメージをなくすことで、リーク不良を大幅に低減できることを実証しました。

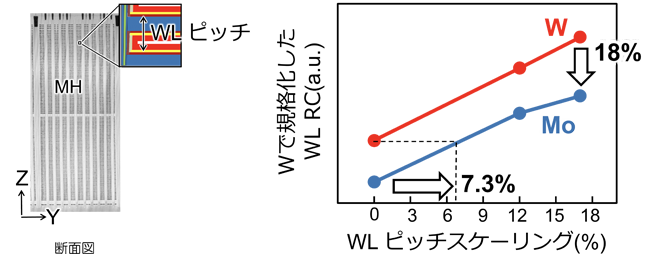

図6に、WLピッチのスケーリング(Z方向のスケーリング)を行った際の、WL MoとWL WのWL RCを紹介します。WL MoのWL RCは、どのピッチでもWL Wに比べて良好で、WLピッチを17%スケーリングした際には、18%の改善が見られます。これは、Moが、Wと比べて抵抗率が低いためです。この結果から、WL Wと同じWL RCまで、WL Moをスケーリングする場合を考えると、WLピッチを7.3%スケーリング可能なことが確認できました。

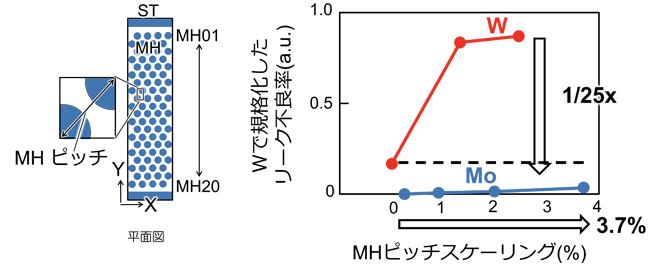

図7に、MHピッチのスケーリング(XY方向のスケーリング)を行った際のWL MoとWL Wのリーク不良率を紹介します。WL Moでは、WL Wと異なり、MHピッチをスケーリングした際のリーク不良率の増加は微量です。WL MoのMHピッチを3.7%スケーリングした際のリーク不良率は、WL WのMHピッチをスケーリングした時の不良率と比べて、25分の1以下で、スケーリングしないWL Wのリーク不良率と比べても十分に低い値を示しています。この結果から、WL Moを採用することで、MHピッチを3.7%以上スケーリング可能であることが確認できました。

これらのXY方向のスケーリング結果から、WL Moは、XY方向およびZ方向のスケーリングにより、同じSiダイ体積で、WL Wに対して16.3%以上のビット密度増加を実現できることがわかりました。

本稿では、3次元フラッシュメモリにおいて、最先端のフッ素フリー WL Moプロセスを用いることによる、WL Wプロセスに対する優位性を実証しました。Mo埋め込み性を最適化することで、XYZスケーリング時のセル絶縁膜や層間絶縁膜へのダメージを低減し、WL Wと比べて、セルの信頼性を劇的に向上させることができることを確認しました。さらに、WL Mo技術により、3次元フラッシュメモリの微細化限界を打破することが可能となることを証明しました。

本成果は、Western Digital Corporationとの共同開発に基づき、2024年6月に開催された国際学会2024 Symposium on VLSI Technology and Circuitsにおいて発表されました[4]。

文献

[1] Yu-jie Song et al., “Modeling and Optimization of Array Leakage in 3D NAND Flash Memory”, 2018 IEEE International Conference on Integrated Circuits, Technologies and Applications (ICTA), 2018, pp.120-121

[2] Tuung Luoh et al., “Tungsten Gate Replacement Process Optimization in 3D NAND Memory”, 2019 Joint International Symposium on e-Manufacturing and Design Collaboration (eMDC) & Semiconductor Manufacturing (ISSM), 2019, pp.1-4

[3] Soochan Chung et al., “Process Improvements for 7th Generation 1Tb Quad-Level Cell 3D NAND Flash Memory in Mass Production”, 2023 IEEE International Memory Workshop (IMW), 2023, pp.17-20

[4] Takashi Fukushima et al., “Fluorine-free Word Line Molybdenum Process for Highly-Scalable and Highly-Reliable 3D Flash Memory”, 2024 IEEE Symposium on VLSI Technology and Circuits, 2024, T6-1.