Please select your location and preferred language where available.

近年、多値フラッシュ・メモリ技術の進歩により、その応用が広まり、より高い性能の要求が高まっています。この要求に対応するため、ワード線やビット線を分割するなどの技術が採用されてきました。しかし、このようなアレイ分割アプローチは、チップサイズの増大につながります。さらに、従来の多値フラッシュ・メモリは本質的に、SLC(1ビット/セル)よりも多くの読出しサイクルを必要とします。

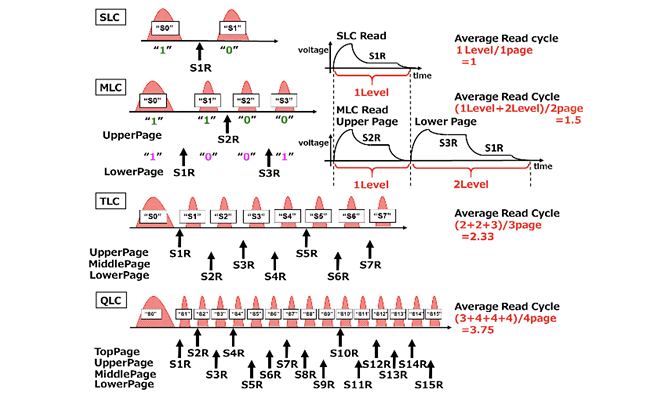

図1は、SLCとMLC(2ビット/セル)の閾値(Vth)分布と、読出し動作でのワード線波形を示しています。

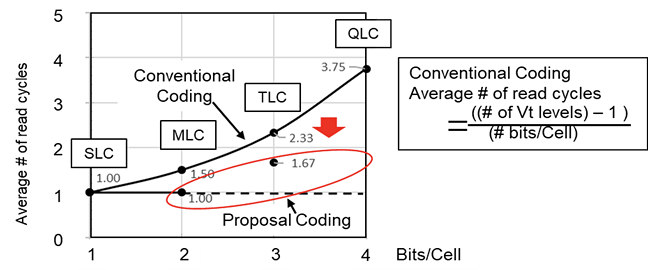

SLCは2つのレベルを区別するために1つの読出しレベルを必要とするが、MLCはUpper-Page*1に1レベルの読出しレベル、Lower-Pageに2レベルが必要なため、平均読出しサイクルは1.5(=(1+2)/2)回となります。さらに、TLC(3ビット/セル)の平均読出しサイクルは2.33(=(2+2+3)/3)回、QLC(4ビット/セル)の平均読出しサイクルは3.75(=(3+4+4+4)/4)回となり、多値化が進むとレベル数が増加し、読出しサイクル数が増え、tRが増大します(図2)。この本質的な課題を軽減するために、本研究では、複数レベルのデータを複数のメモリセルに共用して記憶することで、読出しサイクル数を削減することを提案します[1]。

*1 Pageとは1回の動作で読出されたり書込まれたりするデータ数を表します。通常16kbyte(16k x 8bit)が1pageとなります。MLCでは、2bit/cellの1bitをLowerPage、他の1bitをUpperPageとして扱います。

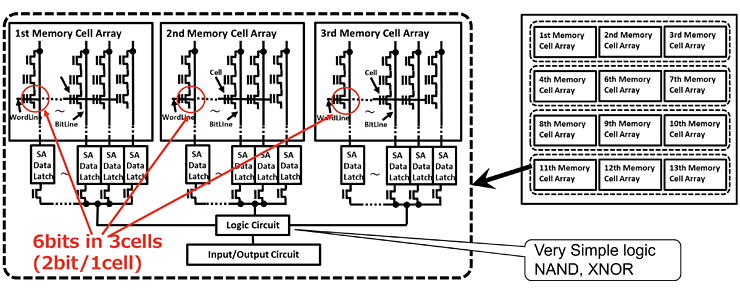

新規多値コーディングを採用したMLCは、3つのメモリセルを組合せ、この3セルで6ビットのデータを記憶します(図3)。平均読出しサイクルは、従来の1.5回から1(=(1+1+1+1+1+1)/6)回と、SLCと同じ回数に削減し、ランダムアクセスをSLCと同等にします。

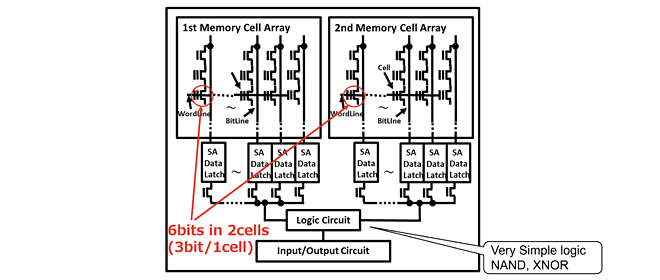

新規多値コーディングを採用したTLCは、2つのメモリセルをペアとし、この2セルで6ビットのデータを記憶します(図4)。平均読出しサイクルは、従来の2.33回から1.67(=(1+1+2+2+2+2)/6)回と28.6%削減し、高速ランダムアクセスとすることが可能です。また、これらの新規多値コーディングは、新しいプロセスや材料の導入なしでセル記憶密度も変えずに、高速化を図ることができます。

本研究は、2024年5月に開催されたIEEEの国際会議IMW (International Memory Workshop) に採択され発表されています。[1]

文献

[1] N. Shibata et al., “Novel Multi-Level Coding and Architecture Enabling Fast Random Access for Flash Memory”, IMW2024, pp. 17-20, May.2024.