Please select your location and preferred language where available.

私たちはBiCS FLASH™ 第8世代においてCBA (CMOS directly Bonded to Array) プロセスを採用しました。CBAプロセスでは、CMOSウェハとセルアレイウェハをそれぞれ最適な状態で別々に製造した後、貼合することで、ビット密度の向上とNAND I/O速度の高速化を実現しています[1]。

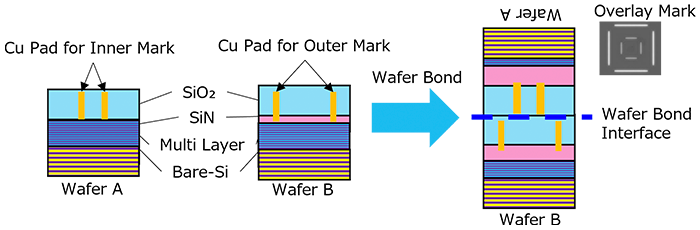

CBAプロセスでは、Cu貼合パッド形成時に重ね合わせ検査用のマークパターンを形成します。ウェハ同士を貼り合わせた後、基板と基板の重ね合わせ精度を計測します。

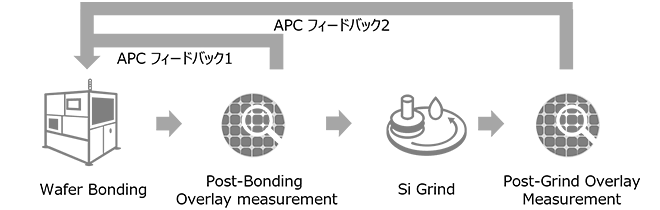

重ね合わせ計測結果より次のLotの重ね合わせ精度がよくなるように補正値を計算して、張り合わせ装置にフィードバックを行います(APC:Advanced Process Control)。

貼合重ね合わせのさらなる精度向上を考慮すると、測定は貼合直後に行う方が良いと言えます。図2は、2つの異なるAPCフィードバックの図です。APCフィードバック1は貼合後の重ね合わせ計測のフィードバックループを示し、APCフィードバック2はSi研磨後の重ね合わせ計測のフィードバックループを示しています。

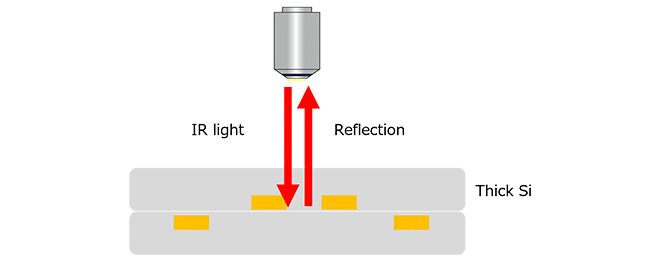

前者は後者に比べ、フィードバックに必要な時間が短く、プロセス変動の追従性が高いため、オーバーレイの改善が容易です。しかし、従来の可視光を用いた重ね合わせ検査装置では、上層に厚いSi層があるためSi研磨前のオーバーレイを測定することができません。そこで我々はKLA社と共同で貼合直後に重ね合わせ測定を行うためシリコン透過型赤外光(IR光)を用いた重ね合わせ検査装置の開発を行いました。

IR光を用いた重ね合わせ検査装置は、図3に示すように、IR光を使用することで、上層のSi層を透過して、重ね合わせマークを反射光で検出します。

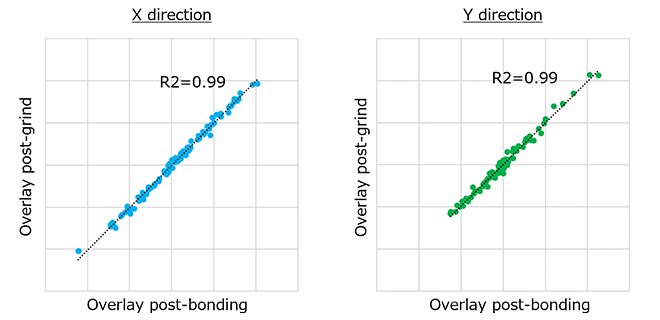

図4は、ウェハ貼合直後にIR光を用いて測定した重ね合わせの結果と研磨後に測定した重ね合わせの結果の相関を示しています。

IR光を用いた重ね合わせ計測結果は、Si研磨後に測定した重ね合わせ結果と良い相関関係を示しました。このことは、貼合直後の重ね合わせ測定において、精度よく重ね合わせ結果を検出できていることを示しており、さらなる貼合重ね合わせ精度向上に寄与することを確認しました。

この成果は国際学会SPIE Advanced Lithography and Patterning 2024で発表されました[2]。

文献

[1] S. Kobayashi et al., “High Performance 3D Flash Memory with 3.2Gbps Interface and 205MB/s Program Throughput based on CBA (CMOS Directly Bonded to Array) Technology”, 69th Annual IEEE International Electron Devices Meeting (2023)

[2] T. Goto et al., “Advanced overlay metrology for wafer bonding applications”, SPIE Advanced Lithography + Patterning 2024 Paper 12955-27