Please select your location and preferred language where available.

トランジスタのゲート絶縁体に強誘電体HfOを利用したFeFETは高速かつ低い書込/消去電圧で駆動が可能で、SCM、ファイルメモリなどの幅広い領域のメモリ候補として期待されています。FeFETの課題の一つはサイクル耐性の改善です。

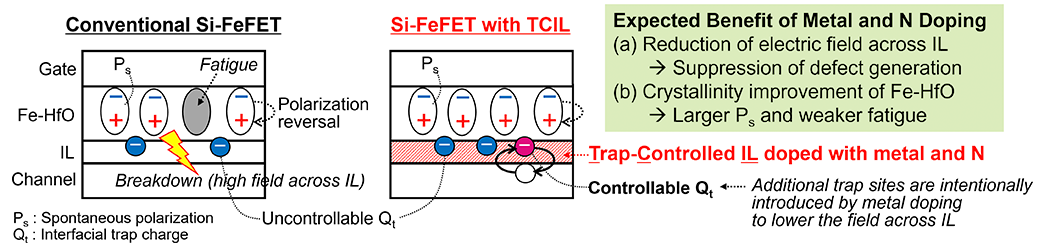

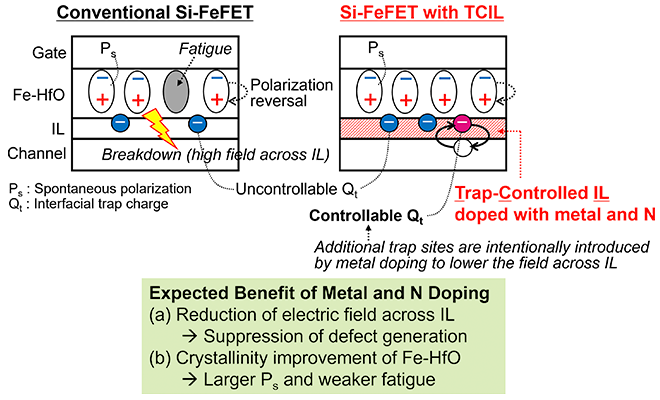

図1は今回提案したサイクル耐性改善に向けたコンセプトです。シリコンをチャネル材料として利用したFeFETではHfOベースの強誘電体材料とチャネルの間に低誘電率のSiOが形成されます(図1.IL)。この界面SiOは書込/消去時に高い電界が印加されることで劣化し、FeFETの特性に悪影響を及ぼします。本論文では、強誘電体の改質と界面層の劣化抑制を実現するため、界面層にメタルと窒素を添加したTrap controlled interfacial layer(TCIL)を導入しました。TCILは書込/消去時に電荷をトラップし、界面層の電界を抑制することでサイクル後のFeFET特性を改善できると期待されます。

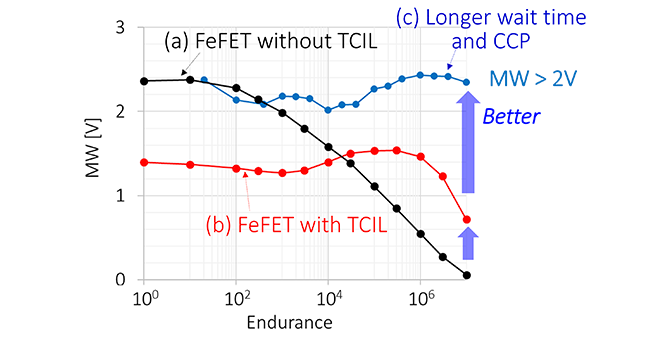

TCILを利用したFeFETのメモリ特性(図2(b))は、メタル添加していないFeFET(図2(a))と比較して初期のメモリウインドウ(MW)が減少するものの、サイクル後のMWが改善します。初期MWの減少は分極反転電荷Psをキャンセルする過剰なトラップ電荷Qtが界面へのメタル添加により増大したためです。

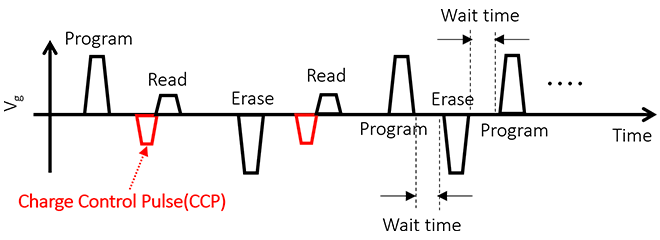

次に、図3に示す界面のQtを調整するチャージ制御パルス(CCP)を読出前に追加してMWを拡大する動作方法を採用しました。Qtの増大を抑制する動作方法と界面へのメタル添加を組み合わせることで、107回後にMW>2Vを達成しました(図2(c))。チャージ制御したFeFETは、サイクル耐性とMWの両方を改善でき様々なメモリアプリケーションに適用できると考えています。

本技術は、2023年12月に米国 サンフランシスコにおいて開催された国際学会IEEE International Electron Devices Meeting 2023(IEEE IEDM 2023)において発表を行いました。

文献

[1] K. Suzuki et al., “High-Endurance FeFET with Metal-Doped Interfacial Layer for Controlled Charge Trapping and Stabilized Polarization”, IEDM, 35-5 (2023).