Please select your location and preferred language where available.

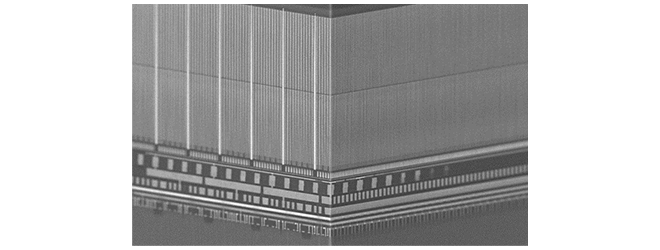

BiCS FLASH™ 第8世代は、1Tb TLC(Triple Level Cell)の製品においてデータ読出し時間40μs、データ書込み速度205MB/s、インターフェース速度3.2Gbpsにメモリ動作を高速化しています[1]。また、ワード線を218層積層し、メモリ密度を18.3Gb/mm2に高めています。TLC製品での18.3Gb/mm2のメモリ密度は、ワード線積層数2xx世代(218層~236層程度)の3次元フラッシュメモリにおいて、最も高密度です。高性能動作・高メモリ密度達成の為、BiCS FLASH™ 第8世代には、CBA(CMOS directly Bonded to Array)とOPS(On Pitch SGD)という新技術が適用されています(図1)。今回は、この2つの技術について紹介します。

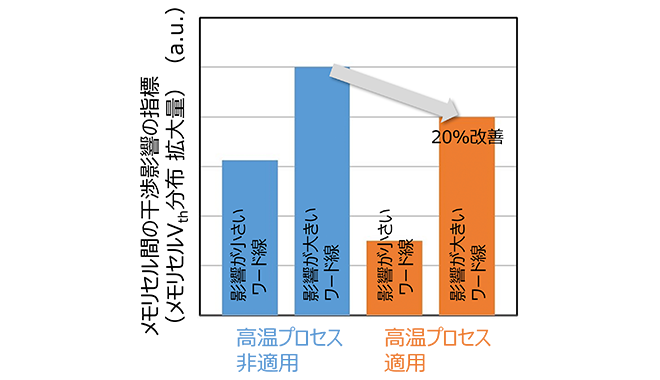

BiCS FLASH™は、情報を記憶するメモリセルアレイとメモリセルアレイを電気的に駆動するCMOS回路から構成されます。従来は、1枚のシリコンウェハ上にCMOS回路とメモリセルアレイの両方を作製していました。従来の作製方式では、CMOS回路とメモリセルアレイとで最適なプロセス条件が異なる為、適用可能なプロセス条件に制限がありました。そこで我々は、CMOS回路とメモリセルアレイを2枚のシリコンウェハに別々に作製し、その後2枚のウェハを貼合するCBA技術を開発しました。CBAでは、CMOS回路とメモリセルアレイのそれぞれにプロセス条件を最適化できる為、メモリ動作の高速化がしやすくなります。例えばBiCS FLASH™ 第8世代では、従来の作製方式ではCMOS回路への悪影響の為に適用できなかった高温プロセスを、メモリセルアレイ作製時に用いることでメモリセル間の干渉を抑制しています(図2)。

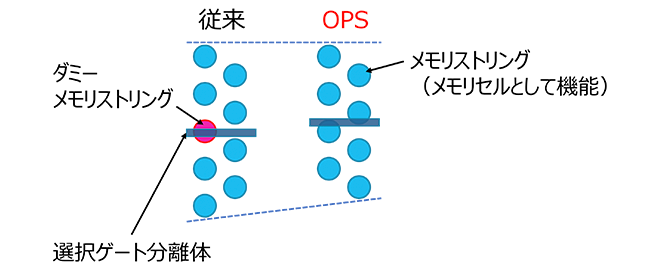

次に、OPSについて説明します。BiCS FLASH™では、ワード線・ビット線・選択ゲートへ印加する電圧を組み合わせることで、電気的にアクセスするメモリセルを選択しています。選択ゲートは、4列のメモリストリング毎に共有されており、各選択ゲートは、絶縁体により電気的に絶縁されています。選択ゲートとメモリストリングの平面方向の位置関係を見てみると、従来は選択ゲートを分離する絶縁体(選択ゲート分離体)を、メモリ機能を持たないダミーのメモリストリングに重ねて配置していました。OPSでは、選択ゲート分離体を、メモリ機能を持つメモリストリング間に配置し、ダミーメモリストリングを削除することで、メモリ密度を高めています(図3)。

これら新規に開発したCBAとOPS技術の適用により、BiCS FLASH™ 第8世代は冒頭に記載の高性能動作・高メモリ密度を実現しています。

本成果は2023年12月に開催された国際学会IEDM(International Electron Devices Meeting)において発表されました。

文献

[1] M. Sako et al., “A 1Tb 3b/Cell 3D-Flash Memory of more than 17Gb/mm2 bit density with 3.2Gbps interface and 205MB/s program throughput”, Proc. IEEE Symp. VLSI Technol., Jun. 2023, C2-1.

[2] S. Kobayashi et al., “High Performance 3D Flash Memory with 3.2Gbps Interface and 205MB/s Program Throughput based on CBA(CMOS Directly Bonded to Array) Technology”, IEEE International Electron Devices Meeting (IEDM), Dec. 2023, 35-2.