Please select your location and preferred language where available.

近年、性能向上(performance)、電力低減(power)、面積削減(area)、コスト削減(cost)のPPACを実現するため、マイクロプロセッサやComplementary Metal Oxide Semiconductor(CMOS)イメージセンサ等の半導体デバイスにおいて銅(Cu)direct bondingプロセス技術を用いた3次元積層デバイスが発表されています[1-4]。今回、Cu direct bondingプロセス技術を基盤として新たにCMOS directly bonded to array(CBA)技術を開発し、BiCS FLASH™ generation 8に適用することで従来技術と比較して3次元フラッシュメモリのPPACが向上し、将来における更なるPPACの改善の可能性を示すことができました。

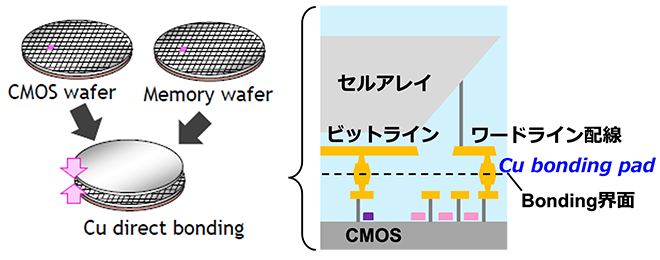

CBA技術は図1に示すように、CMOS周辺回路(以下CMOS)とセルアレイを別々のSiウェハ上に形成した後、表面にCu bonding padを形成、その後Cu direct bondingプロセスを用いてCMOSとセルアレイの表面同士を貼り合わせることにより、Cu bonding pad間を電気的に接続し3次元フラッシュメモリを形成するものです。

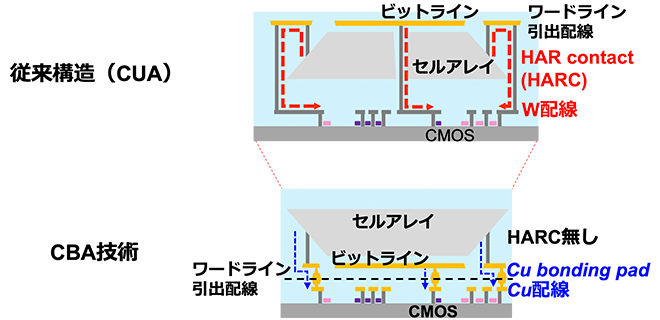

CBA技術を用いることにより、図2に示すように従来のCMOS under Array(CUA)構造と比較して、CMOSとセルアレイ間を接続するために必要となるhigh aspect ratio contact(HARC)が不要となり、配線材料として電気抵抗が低いCuを用いることが可能となります。また、CUAではCMOSを形成した後に連続的にセルアレイを形成する必要があり、セルアレイ形成時における熱負荷がCMOS性能を制限していましたが、CBA技術を用いることにより、CMOSとセルアレイに最適なプロセス温度を用いることが可能となります。その結果、チップ面積の縮減と性能向上が可能となります。

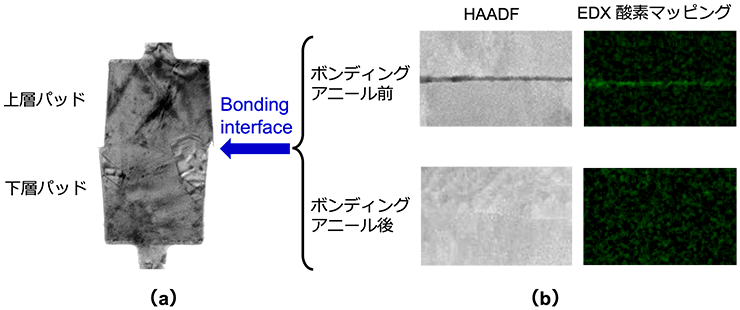

CBA技術では基盤となるCu direct bondingプロセスに対して、Cu bonding padのCu結晶性、Cu-CMPプロセス時の表面段差、貼り合わせ時のCu bonding pad表面状態、アライメント、ウェハ反り等を制御することにより、図3に示すようなCu bonding pad間のズレが小さく、酸素等の不純物が存在しない低抵抗、高信頼を有する特性を実現しました。

(b) Cu bonding pad界面のHAADF*1、EDX*2マッピング像 ©2023 IEEE[5]

*1 High Angle Annular Dark-Field

*2 Energy Dispersive X-ray Spectroscopy

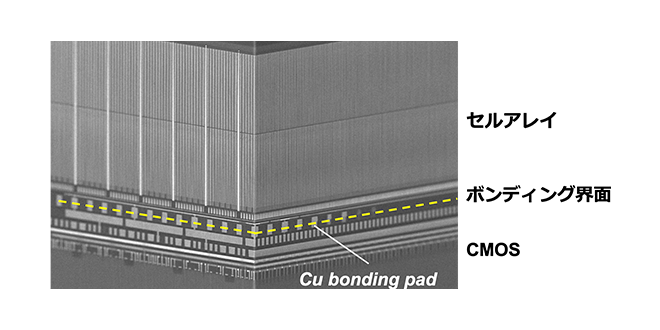

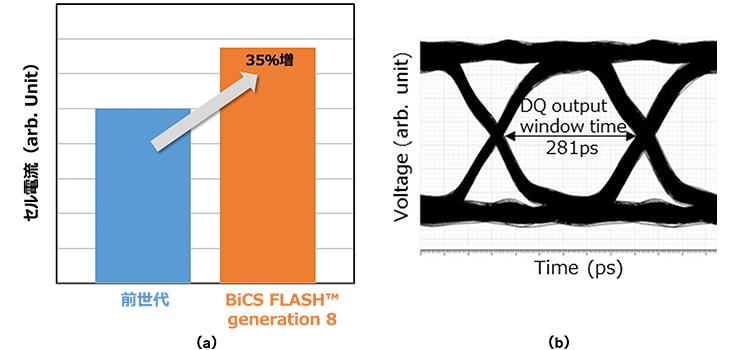

このCBA技術をBiCS FLASH™ generation 8に適用し、図4に示すようなワードライン218層の3次元フラッシュメモリ構造を実現しました。デバイス性能は、図5に示すように従来技術と比較してセル電流が35%向上し、3.2Gbpsのインターフェース性能を実現しました。将来的にはCMOSにHigh-k/Metal Gate(HKMG)を導入し、更なるインターフェース性能を向上させることも可能となります。

また、CBA技術を発展させることにより、2枚以上のCMOS、2枚以上のセルアレイを積層したマルチスタック3次元フラッシュメモリを実現し、より高いビット密度を提供することでBiCS FLASH™におけるPPACの継続的向上が実現可能となります。

(a) セル電流比較及び (b) インターフェース速度特性のアイパターン ©2023 IEEE[5]

本技術は、2023年12月に米国 サンフランシスコにおいて開催された国際学会IEEE International Electron Devices Meeting 2023(IEEE IEDM 2023)において発表を行いました[5]。

文献

[1] S. Arkalgud., “The Era of Advanced Packaging and Hybrid Bonding”, in Tutorial. 2022 IEEE International Electron Devices Meeting (IEDM).

[2] R. Agarwal et al., “3D Packaging for Heterogeneous Integration”, in Proc. 2022 IEEE 72nd Electronic Components and Technology Conference (ECTC)., pp. 1103-1107.

[3] Y. Kagawa et al., “Novel Stacked CMOS Image Sensor with Advanced Cu2Cu Hybrid Bonding”, in Proc. 2016 IEEE International Electron Devices Meeting (IEDM)., pp. 8.4.1-8.4.4.

[4] M. Sakakibara et al., “A Back-Illuminated Global-Shutter CMOS Image Sensor with Pixel-Parallel 14b Subthreshold ADC”, in Proc. 2018 IEEE International Solid-State Circuits Conference (ISSCC)., pp. 80-82.

[5] M. Tagami, “CMOS Directly Bonded to Array (CBA) Technology for Future 3D Flash Memory”, in Proc. 2023 IEEE International Electron Devices Meeting (IEDM).