Please select your location and preferred language where available.

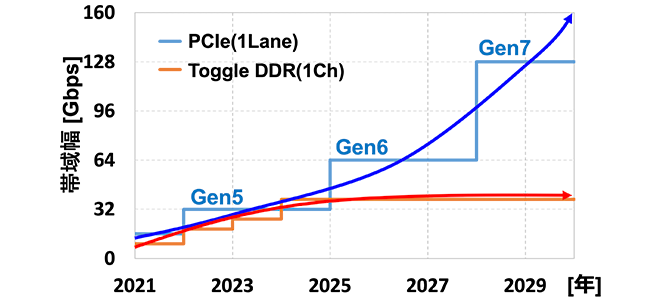

近年、ビッグデータやクラウドコンピューティングの需要が高まる中、高速・大容量のストレージシステムが求められています。SSDに採用されているPCIe®などのホストインターフェースの高速化は着実に進んでいますが、NAND型フラッシュメモリ(NAND)のインターフェース(Toggle DDR)高速化は難しくなっています(図1)。

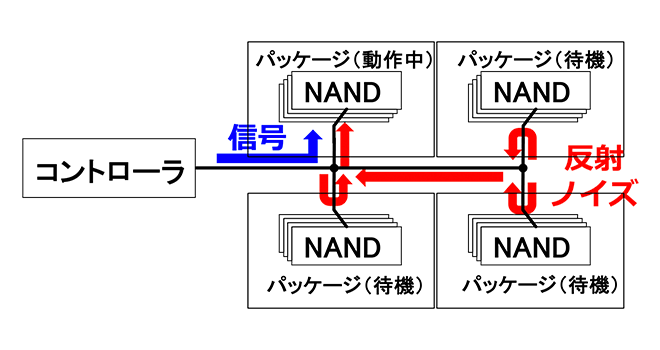

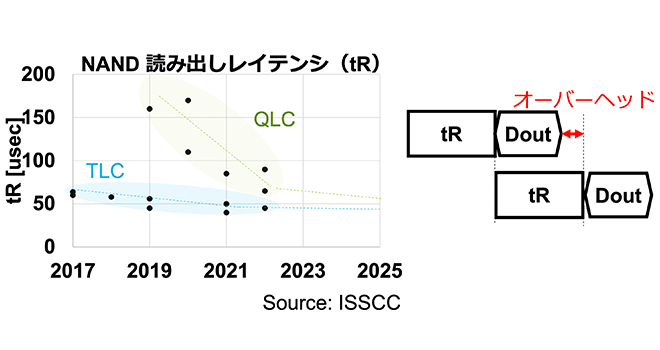

高速化が困難な理由の一つは、インターフェースの高速化とともにシグナルインテグリティが劣化することです。特に大容量SSDの場合、待機状態のNAND型フラッシュメモリを複数積層したパッケージからの反射ノイズにより、シグナルインテグリティの劣化が深刻化します(図2(a))。もう一つの理由は、NANDのインターフェース速度を上げるだけではスループットが向上しないことです。ワードライン層数の増加や多値化(3b/cellや4b/cell[1])により、NAND型フラッシュメモリの読み出しレイテンシ(tR)の縮小は制限される傾向にあります。NANDインターフェースの高速化によりデータ出力時間(Dout)がtRよりも小さくなると、読み出しスループットはtRによって制限されます(図2(b))。

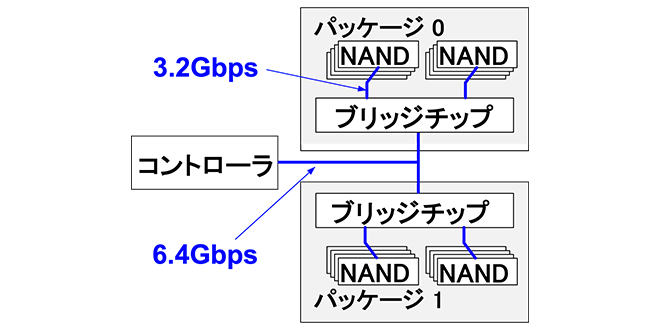

これらの問題を解決するためには、NANDインターフェース速度を維持しながらPCIeのインターフェース速度に追従するマルチチップアクセスのブリッジチップが有効です。今回開発したブリッジチップでは、プリント基板上の各チャネルに複数のパッケージを搭載しても、コントローラとの間のインターフェースはNANDインターフェースの2倍の速度を実現しています(図3)。

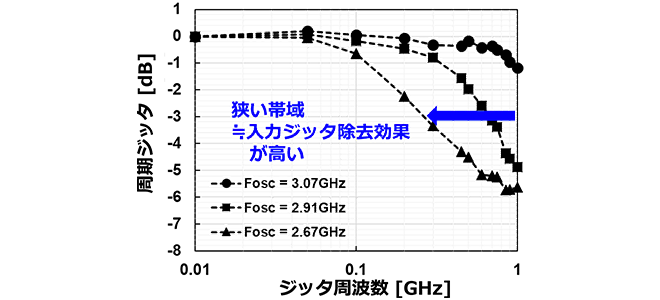

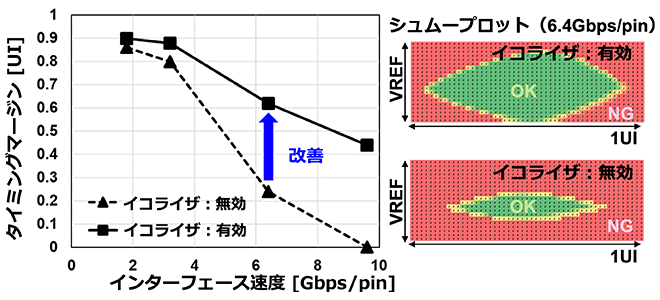

ブリッジチップには、“NANDインターフェースの性能を向上させるための高いジッタ除去効果を持つインジェクションロックベースのPLL”、“プリント基板の分岐構成に起因する反射ノイズを補正するイコライザ”を搭載しています。インジェクションロックベースのPLLは入力信号の立ち上がりエッジと立ち下がりエッジに電流を注入する方式により、プルインレンジを大幅に拡大します。この広いプルインレンジにより、ロック前のVCOの周波数(FOSC)を入力CLK周波数(FCKIN)より更に低く設定することができるため、入力周期ジッタ伝達関数の-3dB帯域幅をより狭くすることができます(図4(a))。受信回路に実装された4タップの判定帰還型イコライザは、反射ノイズを補正し、二分岐構成チャネルのアイ開口を大きく改善させることができます(図4(b))。

12nmのCMOSプロセスで開発されたブリッジチップは、読み出し動作において6.4Gbps/pin、2.85pJ/bのI/Oエネルギー効率を実証しています。また、ブリッジチップと8個の1Tb NANDダイを組み込んだNAND型フラッシュメモリマルチチップパッケージ(NAND MCP)は、プリント基板の2分岐構成でNANDインターフェースの2倍の速度でコントローラを模擬したFPGAとのデータ転送を実証しています。

我々が開発した倍速化技術を適用し、NAND MCPのインターフェース速度を倍速化することで、プリント基板上の配線面積とコントローラ上のシリコン面積を削減することができ、システムコストの低減につながります。また、多分岐した環境下でもNAND MCPのインターフェース速度を維持できるため、コントローラ1チャネル当たりのNAND接続数を増やすことができ、ストレージシステムの容量と性能をスケーラブルに向上させることができます。

本成果は2023年11月に開催された国際学会2023 IEEE Asian Solid-State Circuits Conference(A-SSCC)において発表されました。

文献

[1] J. Yuh, et al., “A 1-Tb 4b/Cell 4-Plane 162-Layer 3D Flash Memory with a 2.4-Gb/s I/O Speed Interface,” ISSCC, pp.130-132, Feb. 2022.