Please select your location and preferred language where available.

3次元フラッシュメモリのチップサイズ縮小と高速化のため、我々はBiCS FLASH™ 第8世代においてCBA(CMOS directly Bonded to Array)プロセスを採用しました。CBAプロセスではCMOS(Complementary Metal Oxide Semiconductor)素子とメモリセルアレイを独立したウェハに別々に形成した後、それぞれのウェハ表面に形成したCu(銅)貼合パッド間を接続させてCMOS素子とメモリセルアレイを電気的に接合します[1]。CBAプロセスを採用することで、CMOS素子とメモリセルアレイを最も短い配線で接続することができ、チップサイズ縮小が実現できます。さらにCMOS素子の熱履歴をメモリセルアレイ形成工程から独立して最適化することができ、デバイスの高速化を実現できます。

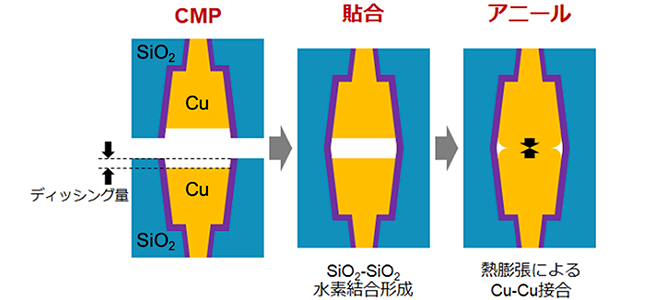

CBAプロセスでは、シリコン酸化膜間に水素結合を形成してウェハ同士を貼り合わせた後、アニールによりCuを熱膨張させてCu-Cu接合を形成します(図1)。このため、CMP(Chemical Mechanical Polishing)工程で形成されるディッシング(Cuの凹み)量をCuの熱膨張量以下に低減することが必要となります。

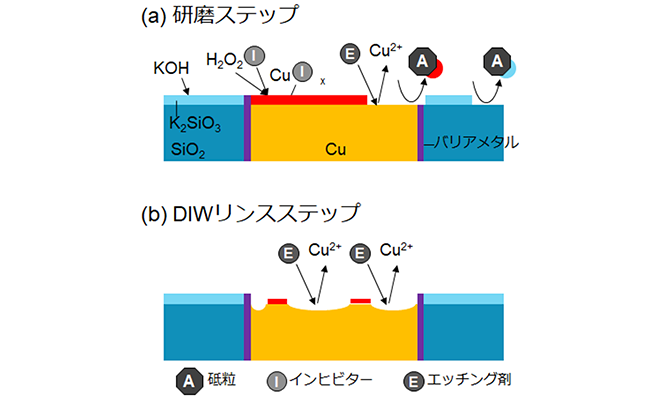

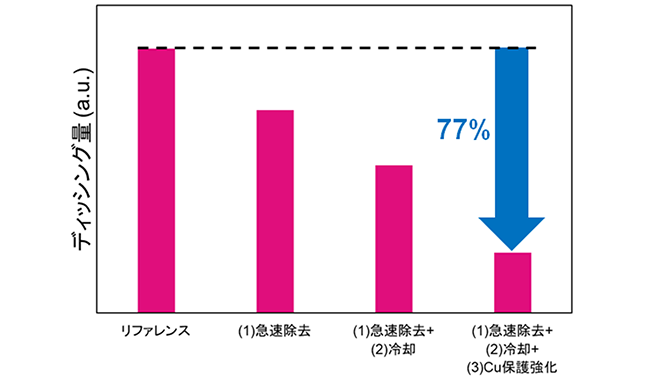

我々はディッシングが研磨ステップ後のDIW(De-ionized Water)リンスステップ中のケミカルエッチングにより増大するという仮説を構築しました(図2)。具体的には、スラリー中に含まれるエッチング剤が研磨ステップ後も残留し、DIWリンスステップ中にインヒビター(Cu表面保護剤)により十分保護されていないCu表面をエッチングするというメカニズムです。この仮説に基づき、(1)大量のDIWによるエッチング剤の急速除去、(2)冷却によるケミカルエッチング抑制、(3)インヒビターによるCu表面保護強化、の3つのディッシング低減アプローチを提案し、ディッシング量を77%低減することに成功しました(図3)。ディッシングの低減により、CBAプロセスに必要とされるCu-Cu接続の電気的歩留を達成することができました[2]。

この成果は国際学会ICPT 2023で発表されました。

文献

[1] S. Sivaram and A. Ilkbahar, “Searching for Nonlinearity: Scaling Limits in NAND Flash”, 2023 IEEE Symposium on VLSI Technology and Circuits, PL2-2 (Plenary).

[2] T. Watanabe et al., “Cu dishing reduction on CBA (CMOS directly Bonded to Array) process for 3D flash memory”, 2023 International Conference on Planarization/CMP Technology(ICPT), O29.