Please select your location and preferred language where available.

新規高速メモリの候補としてFeFET(Ferroelectric Field Effect Transistor)が注目を集めています。FeFETはトランジスタのゲート絶縁膜に強誘電体膜を使った構造で、ゲート電圧で強誘電体の分極方向を制御でき、分極方向に応じてトランジスタの閾値電圧Vthが変化する不揮発性メモリです。中でも、強誘電体膜としてHfO2を使ったHfO2-FeFETは、低電圧・高速動作が可能なうえ、CMOSプロセスとの整合性が良いというメリットがあります。

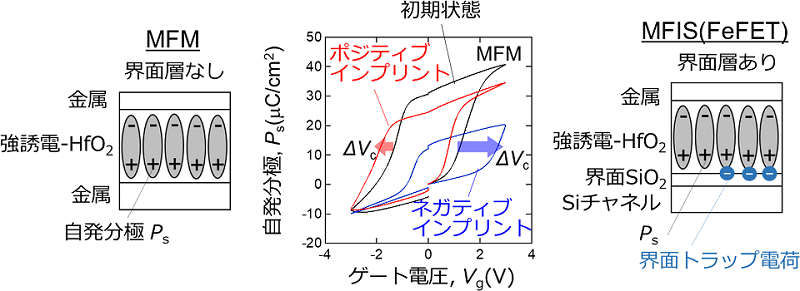

私たちはFeFETの信頼性課題の一つであるインプリントに着目しました。インプリントは分極状態保持中に分極反転に必要なゲート電圧(抗電圧Vc)が変化する現象です(図1)。キャパシタ構造(MFM*1)ではインプリントの影響を受けて自発分極Psとゲート電圧Vgの関係(ヒステリシス)が左右にシフトします。FeFET(MFIS*2)は、低誘電率の界面SiO2があるため、インプリントによるVcシフトだけでなく界面トラップ電荷による内部電界の変化も考慮する必要があります。しかしながら、測定で得られる電荷は自発分極Psとトラップ電荷が混ざった状態で観測されます。そこで、私たち独自の手法[1]で、FeFETの自発分極Psとトラップ電荷を実験で定量的に切り分けて抽出し、FeFETにおけるインプリントの描像を明らかにしました。

- Metal-Ferroelectric-Metal, 金属-強誘電体-金属

- Metal-Ferroelectric-Insulator-Semiconductor, 金属-強誘電体-絶縁体-半導体

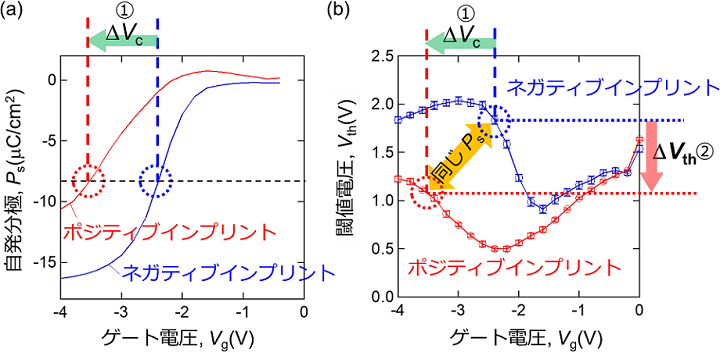

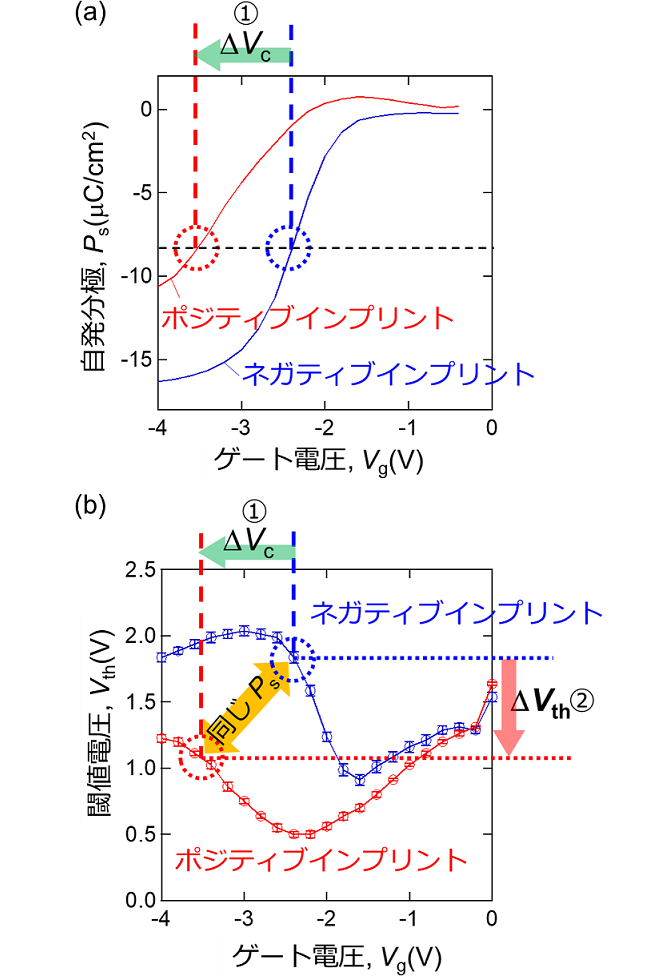

図2(a)は私たちが独自の手法[1]で抽出したMFIS構造の自発分極Psのゲート電圧依存性です。同じPsが得られるVcがネガティブインプリントからポジティブインプリントへシフトし、MFIS構造においても典型的なインプリントの振る舞いが確認されました(①)。図2(b)はMFIS構造のVthのゲート電圧依存性です。VthにはPsとトラップ電荷両方の情報が含まれています。図2 (a)で分かったポジティブインプリントとネガティブインプリントの同じPsとなるゲート電圧を図2(b)で比較すると、異なるインプリントの状態間でVcシフト(①)に加えてVthシフト(②)も見られました。今回の実験で新たにMFIS構造では分極状態が同じにもかかわらず、2つのインプリント状態で異なるVthを取ることが分かりました。

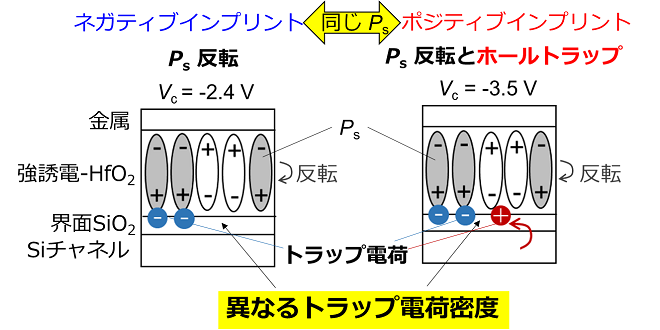

上述した通り①のVcシフトが生じる原因はMFM構造でも観測されたインプリントです。②の分極状態が同じにもかかわらずVthが異なる理由は、界面トラップ電荷の差で説明できます。図3はVcにおけるネガティブインプリントとポジティブインプリントの分極状態とトラップ電荷の模式図です。ポジティブインプリントはネガティブインプリントと比較してVcの絶対値が高電圧化します。より絶対値の高いVcを印加することで、界面近傍に強誘電体の分極で生じた電荷と逆の極性のホールがトラップされます。このため、Vcの異なるネガティブインプリントとポジティブインプリントの状態は消去後に界面に生じたトラップ電荷密度が変わりVthの変調が観測されたと考えられます。

FeFETではインプリントによるVcシフトに加えて、トラップ電荷によるVth変調が起こることを見出しました。この結果はFeFETの信頼性向上に向けた有益な知見であると考えます。

本成果は2023年9月に開催された国際学会SSDM(International Conference on Solid State Devices and Materials)において発表されました[2]。

本稿は、文献[2]©2023 Japan Society of Applied Physicsから図面等一部抜粋&再構成したものです。

文献

[1] R. Ichihara et al., VLSI2020, TF1.2.

[2] Y. Yoshimura, et al., Ext. Abstr. Solid State Devices and Material, 2023, p. 375.