Please select your location and preferred language where available.

概要

メタルアシスト材料を用いたSiチャネル単結晶化技術を3次元フラッシュメモリへ適用し、世界で初めてセルアレイ動作を実現しました。本技術を用いることで、従来の多結晶Siチャネルに対して、チャネル中の粒界密度が低減し、その結果チャネル中のトラップ密度が低減することで、チャネル抵抗の低減、しきい値分布幅の改善、QLC (quadruple level cell) 動作時のセル信頼性改善を実証しました。

緒言

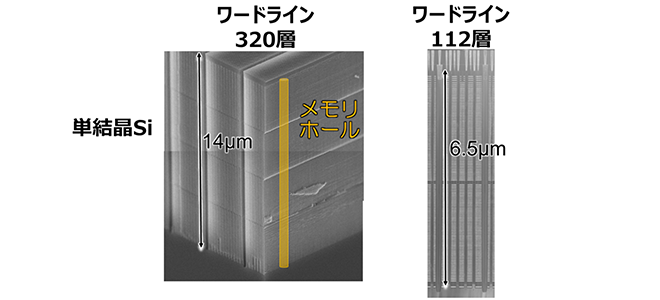

メモリデバイスに対する高Bit密度化、大容量化の市場要求は近年一層強まり、3次元フラッシュメモリでは、セル積層数の増加、ゲートピッチの縮小、さらなる多値化などにより対応してきました。しかし、積層数増加に伴うチャネル抵抗の増加や、多値動作時のセル信頼性確保が問題となってきています。そこで、Siチャネルの結晶粒界を減らしてチャネル中のトラップ密度を低減させることで、チャネル抵抗低減や多値動作時のセル信頼性改善を期待し、メタルアシスト単結晶化(metal-induced-lateral-crystallization: MILC)技術の開発を進めています[1][2]。今回MILC技術を用いて、ワードライン320層までの3次元構造においてチャネル単結晶化に成功し(図1)、従来の1/10以下のチャネル抵抗、40%超のランダムテレグラフノイズ低減、24%のしきい値分布幅を低減した良好なQLC (quadruple level cell) 動作を実証しました[3]。

MILC技術を用いた高積層3次元フラッシュメモリのチャネル単結晶化

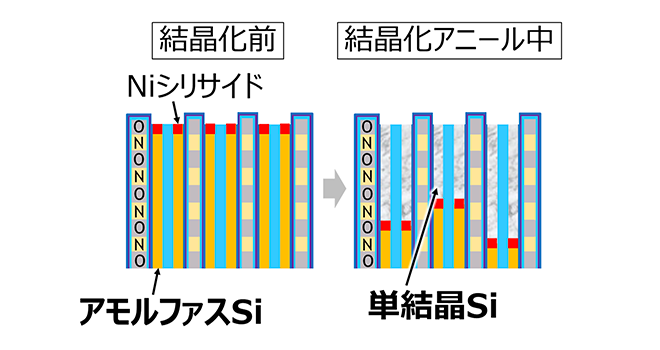

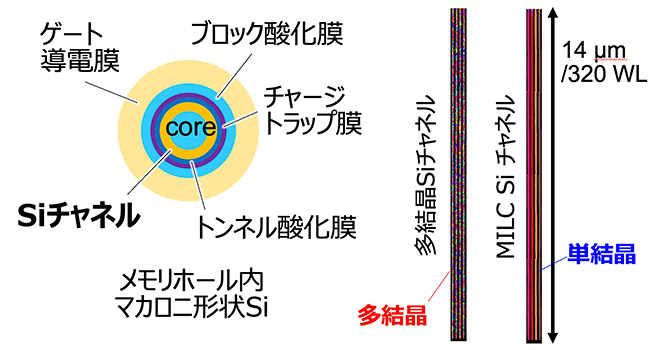

MILC技術では、Niシリサイドをメモリホールの最上層から最下層に向けて拡散させることで、Siチャネルを単結晶化しています。途中にNiシリサイドの拡散を阻害するものがあると、メモリホールの最下層まで単結晶化を進めることができません(図2)。本研究では、Siチャネル層の成膜方法とNiシリサイドを拡散させるための熱処理の最適化を行い、阻害物の生成を抑制することに成功しました。その結果、ワードライン320層のメモリホール内に形成されたマカロニ形状[4]のチャネル長14μmのSiチャネルを完全に単結晶化することができました(図3)。

メモリホール内チャネル単結晶化による3次元フラッシュメモリのチャネル抵抗低減

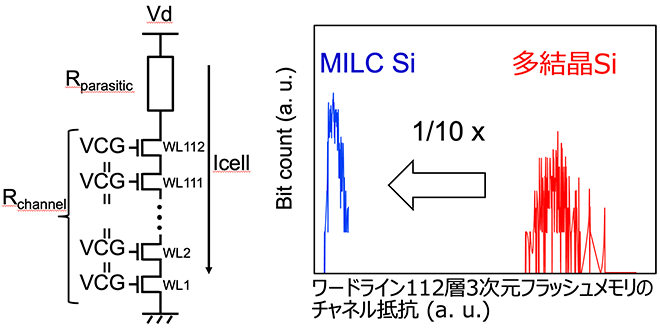

多結晶Siチャネルには粒界が多数存在し、その粒界中には多くの格子欠陥があります。これらが電子に対してトラップ準位を形成し、電子散乱源となり、チャネル抵抗を増大させる要因となります。粒界密度が極限まで低減された単結晶Siチャネルでは、チャネル抵抗の大幅な低減が期待できます。ワードライン112層の3次元フラッシュメモリにMILC単結晶Siチャネルを適用し、多結晶Siチャネルと比較して約1/10までチャネル抵抗が低減されることを実測より確認しました。

MILC単結晶Siチャネルを用いた3次元フラッシュメモリのQLC動作における信頼性改善

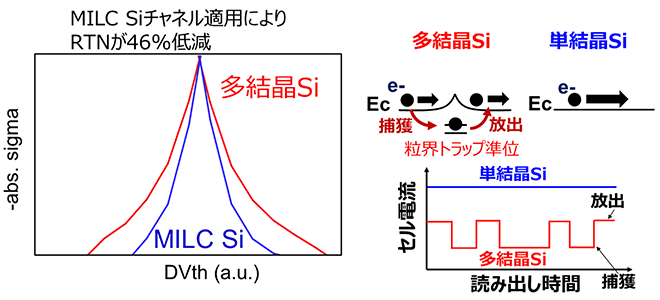

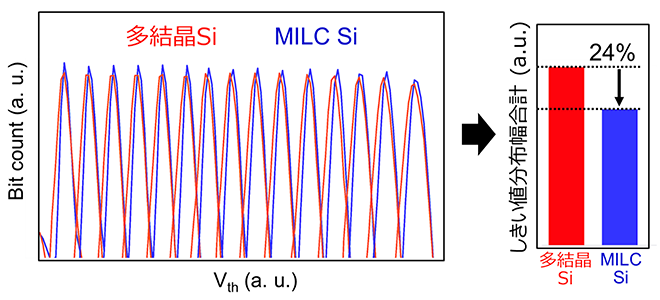

MILC単結晶Siチャネルの採用は粒界に存在する電子トラップに起因したランダムテレグラフノイズ(random telegraphic noise: RTN)の低減にも効果的で、実測で46%RTNを低減できました(図5)。RTNは金属酸化膜半導体電界効果トランジスタ(metal-oxide-semiconductor field-effect transistor: MOSFET)のしきい値電圧をランダムに変動させ、メモリ特性を悪化させます。RTN低減に伴い、多結晶Siチャネルと比較してデータ書き込み時のしきい値分布幅の合計が24%低減された良好な4ビット/セル(quadruple-level cell: QLC)動作を確認しました(図6)。

まとめ

3次元フラッシュメモリに、MILC単結晶Siチャネルを適用することで、従来の多結晶Siチャネルと比較して、約10倍のチャネルコンダクタンス改善、40%以上のランダムテレグラフノイズ低減、24%しきい値分布幅を低減した良好なQLC動作を実現することができました。MILC単結晶Siチャネルは、3次元フラッシュメモリのさらなる高積層化、高Bit密度化、高信頼性化のキーテクノロジーであることが実証されました。

本成果は2023年6月に開催された国際学会2023 Symposium on VLSI Technology and Circuitsにおいて発表されました[3]。

文献

[1] H. Miyagawa et. al., “Metal-Assisted Solid-Phase Crystallization Process for Vertical Monocrystalline Si Channel in 3D Flash Memory”, 2019 IEEE International Electron Devices Meeting, pp.650-653.

[2] S. Ramesh et. al., “Understanding the kinetics of Metal Induced Lateral Crystallization process to enhance the poly-Si channel quality and current conduction in 3-D NAND memory”, 2021 IEEE International Electron Devices Meeting, pp. 210-213.

[3] N. Ishihara et. al., “Highly Scalable Metal Induced Lateral Crystallization (MILC) Techniques for Vertical Si Channel in Ultra-High (> 300 Layers) 3D Flash Memory”, 2023 IEEE Symposium on VLSI Technology and Circuits, T7-1.

[4] Y. Fukuzumi et. al., “Optimal Integration and Characteristics of Vertical Array Devices for Ultra-High Density, Bit-Cost Scalable Flash Memory”, 2007 IEEE International Electron Devices Meeting, pp.449-452.