Please select your location and preferred language where available.

フラッシュメモリは構造の微細化と3次元化に加えて、多値化[1]によって記録密度を向上させており、1bitのデータを記憶するコスト(以下ビットコスト)は低下しています。特に多値化は、同じメモリセル密度のままで記録密度を向上させることができるため、低コスト化の手法として大きな効果を持ちます。我々の先行研究により、3Dフラッシュメモリのチャネルの結晶性を良くして、マイナス200度の極低温で動作させるとストレージの特性が大幅に向上し、7ビットセル(7bit/cell)の記録密度が達成できることが分かり、国際学会で報告しています。[2]

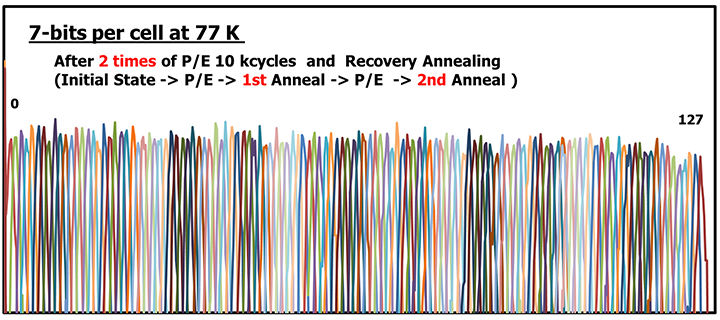

今回は持続可能な社会の実現に向けたさらなるビット低コスト化の手法として、回復アニール(熱処理)による再生利用の検討をしました。フラッシュメモリには書き換え寿命があります。データをメモリセルに蓄積した電荷量として記録しており、データを書き込み/消去する動作では高い電圧を加えてその電荷の出し入れをします。書き込み/消去を繰り返すことにより、読み出し時のノイズが増えることやデータの保持特性が悪化するため3Dフラッシュメモリを用いたSSDではデータの書き換え可能回数に制限があります。我々は極低温と単結晶チャネルを用いた3Dフラッシュメモリの書き込み/消去動作によるストレージの特性劣化を評価し、回復アニールを適用する実験を行いました。その結果、メモリセルに適切なデータを書き込んで200℃で3時間の熱処理を行うことで、完全に特性の回復ができることが分かりました。この回復現象は繰り返して用いることが可能です。書き込み/消去による特性劣化とアニールによる回復を2回繰り返したサンプルにおいて、7ビットセルの動作を行った結果を示します(図1)。合計2万回のデータの書き換えでも初期状態と変わらない128個(7ビットに相当)の閾値分布を形成できています。

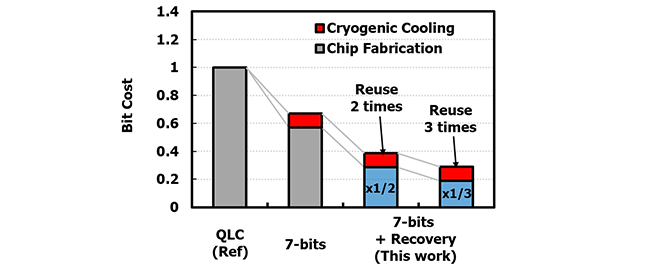

我々は、チップ冷却を含めたストレージシステムのコストを見積もりました。この回復アニールによる繰り返し再生利用とマイナス200度の極低温動作を組み合わせることで、現行のQLC等に対して半分以下のビットコスト低減が可能であり、製造時のCO2排出量の削減にも寄与できるため、持続可能な社会の実現に大きく貢献すると考えています。(図2)。

本稿は2023年6月に開催された国際会議VLSI Symposium(Symposium on VLSI Technology and Circuits)に発表された文献[3]から図面等一部抜粋&再構成したものです。 本研究のコスト見積りに用いた極低温冷却システムの仮想設計はナガセテクノエンジニアリング株式会社が行いました。

文献

[1] フラッシュメモリの大容量化を実現する「多値化技術」とは

[2] H. Tanaka et al., IMW 2022, pp. 1-4.

[3] VLSI 2023 to be published