Please select your location and preferred language where available.

近年電界効果トランジスタのゲート絶縁膜に強誘電体を用いたFeFET (Ferroelectric FET)が次世代メモリの有力候補として注目されています。FeFETは強誘電膜の持つ自発分極の反転によるVth(閾値電圧)の変調を利用した不揮発メモリの一種です。特に強誘電性HfO2を用いたFeFETは低電圧・高速動作が可能なうえ、CMOSプロセスとの整合性が良いというメリットを持ちます。

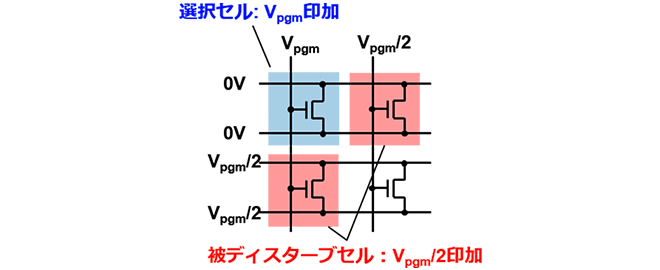

メモリ素子を製品化する際には集積度を上げるために素子はアレイ状に並べられ、複数の素子が同じ配線を共有します(図1)。このようなアレイ構成では、例えばある素子に電圧を印加して情報を書き換えるとき、配線を共有する素子に低電圧のストレスが必ず印加されます。この低電圧ストレスが長時間加わることによって、意図せず自発分極の反転が生じる(ディスターブ)ことがあります。ディスターブによる保存した情報の喪失を防ぐためには、分極反転メカニズムの深い理解が求められます。

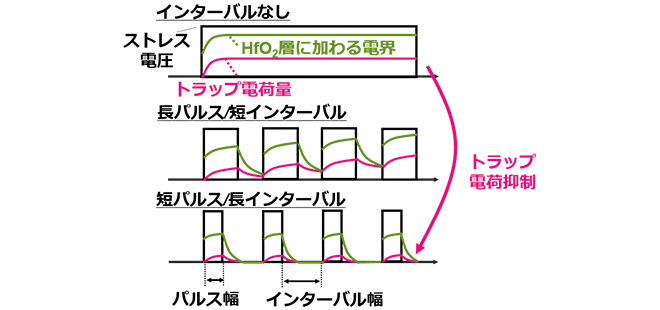

今回私たちはFeFETにおける分極反転と電荷トラップの相互作用に着目しました。低電圧ストレスにおける電荷トラップとの相互作用がどのように分極反転に影響を与えるのか調査し、その結果を元にディスターブを抑制する新規動作手法を提案しました。FeFETでは自発分極の反転だけでなく、その効果を打ち消す極性の電荷トラップ・デトラップが生じることが知られています(図2)[1]。その中でも短時間で放出される不安定な成分は強誘電膜に印加される電界を動的に強めると考えられます。そこで不安定成分のトラップを抑制、デトラップを促進することによってディスターブを防げるのではないかと考えました。

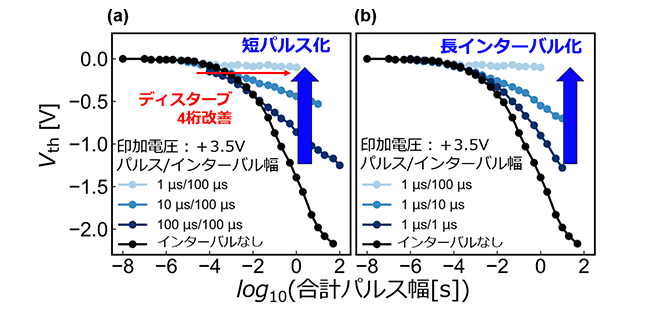

この提案を検証するために、低電圧ストレスを印加電圧0Vのインターバルで分割したシーケンスでストレスを印加し、パルス幅とインターバルを変えたときに分極反転特性がどのように変化するのか調べました(図3)。

図4(a)からパルス幅を短くするほどVthの変化が抑えられること、図4(b)からインターバルを長くするほどVthの変化が抑えられることが判明しました。予想通りトラップ電荷の制御がディスターブ抑制に効果的な技術であると言えます。今回評価した範囲ではパルス幅1μs、インターバル100μsのシーケンスで最もVthの変化を抑えることができ、インターバルを導入しない場合に比べてVthが変化し始めるストレス時間(合計パルス印加時間)を4桁以上も改善することに成功しました。

本稿は、2023年3月に開催された国際学会IRPS(International Reliability Physics Symposium)で発表された文献[2]から図面等一部抜粋&再構成したものです。

文献

[1] R. Ichihara, et al., VLSI2020, TF1.2.

[2] T. Hamai, et al., IRPS2023, 6A1.