Please select your location and preferred language where available.

Twin BiCS FLASH

~3次元フラッシュメモリの更なる大容量化を実現する半円型構造セル~

2020年1月10日

円型セルのゲート電極を分断して半円型にすることでセルサイズを縮小し、より少ないセル積層数で高いビット密度を実現するセル構造 を開発しました。導電体電荷蓄積層(Floating Gate/FG)を用いたセル設計の改良により、円型セルよりも小さいセルサイズで、高い書込スロープと広い書込/消去ウィンドウを取得することに初めて成功しました。そして、この新規構造セルは、ビット密度の増大に有効であるセルの超多値化に向けて、有望な候補であることを示しました。

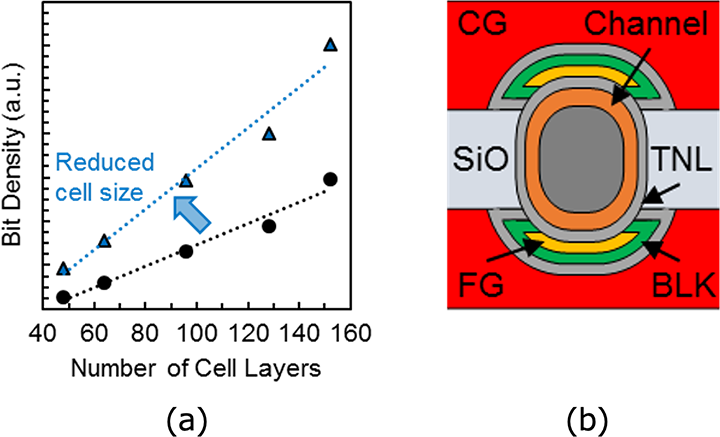

これまで、BiCS FLASH™に代表される3次元フラッシュメモリでは、セル積層数を増やし、高アスペクト比の加工プロセスの適用により、大容量かつ低ビットコストを実現しています[1]。しかし、製品のセル積層数は100層を超え始めており[2]、加工形状/寸法の制御、高プロセススループットの確保等が難しくなってきています。そこで、従来の円型セルのゲート電極を分断して半円型にすることでセルサイズを縮小し、より少ないセル積層数で高いビット密度を達成する技術(図1)を、世界で初めて*1開発しました。また、セル構造/プロセスの最適化により、書込速度の向上に重要となる高い書込スロープ*2と広い書込/消去ウィンドウ*3を、円型セルよりも小さいセルサイズで実現しました。

半円型セル構造

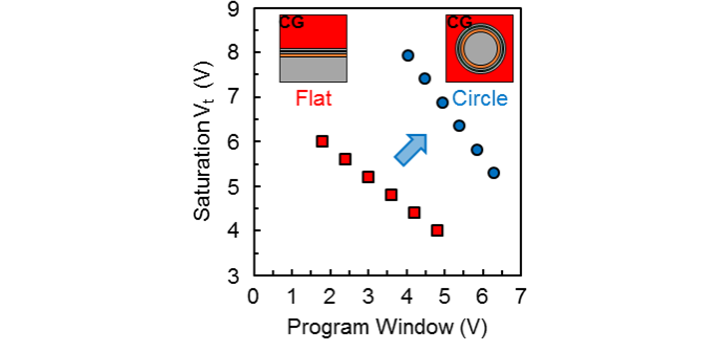

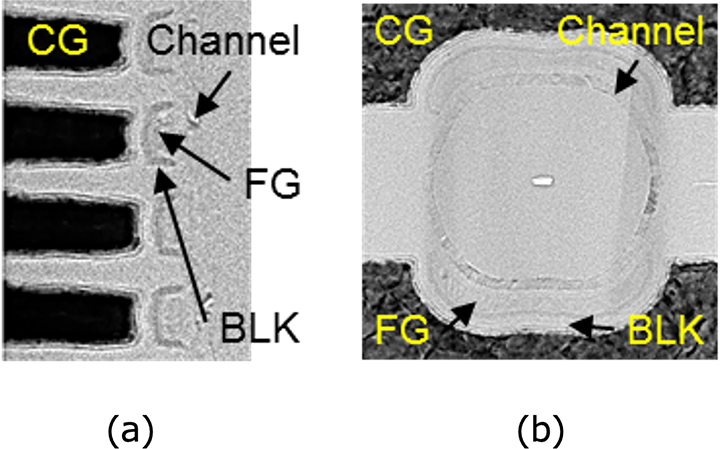

円型セルはフラットセルと比較して、曲率効果[3]により書込ウィンドウを確保し、書込飽和*4を抑制できます(図2)。曲率形状によって、トンネル膜を介する電荷の注入効率が高くなり(書込ウィンドウ増)、同時にブロック膜のリーク電流が低減することで、注入された電荷がブロック膜に抜けること(書込飽和)を抑えます。この新規セル構造は、(図3)に示すように曲率効果の利点を生かす半円形状を採用しており、さらに電荷蓄積層は電荷の捕獲効率が高い導電体(Floating Gate/FG)、ブロック膜にはリーク電流を下げるための高誘電率絶縁体を用いています。導電体電荷蓄積層は各セルで分離されており、上下セル間で絶縁体電荷蓄積層が繋がっているチャージトラップ(Charge Trap/CT)セルと比較して、セル間の電荷移動を抑制することができます。

半円型セル特性

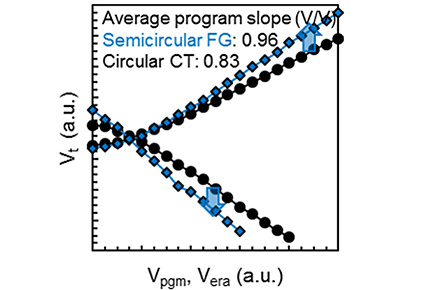

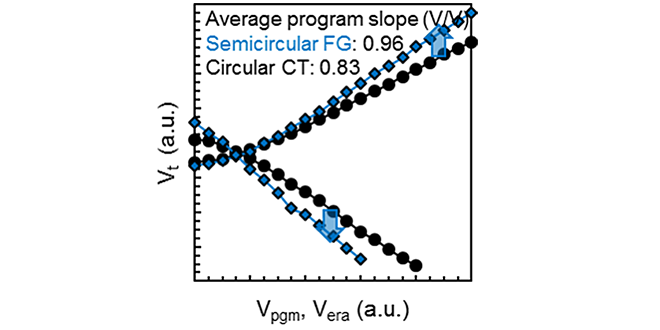

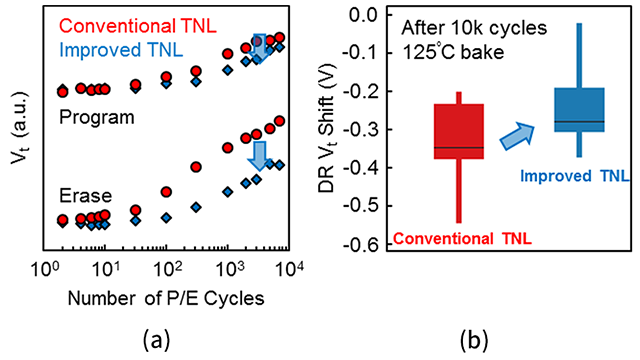

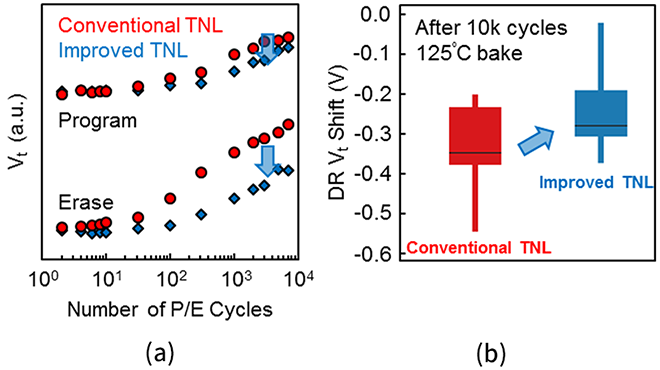

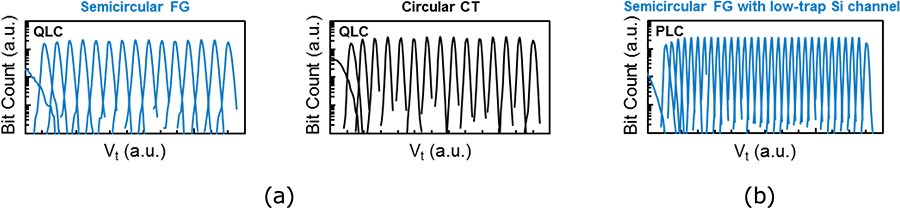

導電体電荷蓄積層と高誘電率ブロック膜の適用によって、(図4)に示すように円型セルに比べて高い書込スロープと広い書込/消去ウィンドウを、縮小したセルサイズにて実証することに初めて成功しました。また、トンネル膜の成膜プロセス含めた膜質及び界面特性を改善することで、書込/消去ストレス後のセル特性変動を低減することができます(図5)。これらの特性改善技術により、セルサイズを縮小した半円型セルで、Vt分布のシミュレーションを行うと、従来の円型セルと同等の4ビット/セル(Quadruple-Level Cell)でのVt分布、さらに低トラップのシリコンチャネルを組み合わせることで5ビット/セル(Penta-Level Cell)でのVt分布が確認できました。これにより大容量化に有効なセルの超多値化に有望な構造であることがわかりました (図6)。

従来の円型セルのゲート電極を分断して半円型にし、セルサイズの縮小に加えて超多値化を実現する新規構造セルを開発することで、少ないセル積層数で高いビット密度を達成する技術の可能性を明示しました。今後もセル設計の改良を実施し、実用化に向けて研究開発を継続していきます。

- 2019年12月現在、当社調べ

- 印加電圧あたりの閾値電圧(Vt)変動量

- 消去から書込までの閾値電圧差

- 印加電圧あたりの閾値電圧変動量が減少する特性

参考文献

[1] H. Tanaka, et al., “Bit cost scalable technology with punch and plug process for ultra high density flash memory”, Symp. VLSI Tech. Dig., p. 14, 2007.

[2] C. Siau, et al., “A 512Gb 3-bit/cell 3D flash memory on 128-wordline-layer with 132MB/s write performance featuring circuit-under-array technology”, ISSCC Tech. Dig., p. 218, 2019.

[3] S. Amoroso, et al., “Semi-analytical model for the transient operation of gate-all-around charge-trap memories”, IEEE Trans. Electron Devices, p. 3116, 2011.