Please select your location and preferred language where available.

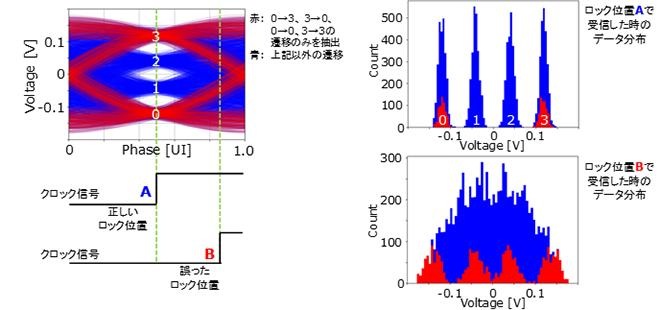

近年、データ通信の高速化に対する要求を満たすために従来のNRZ*1方式に代わりPAM4*2方式が採用されるようになってきました。また、高速データレートにおいても高ロスチャネルに対応するため、デジタルイコライザー機能を持つADC*3-DSP*4ベースの受信機が採用されてきています。このようなADC-DSPベースの受信機の多くではクロック信号を再生する際、アナログベースの受信機の多くで用いられているボーレート*5の2倍で動作するCDR*6の代わりにMueller-Müller CDRのようなボーレートで動作するCDRが使われています。しかし、従来のボーレートCDRではPAM4信号からクロック信号のロック位置を決定する際、PAM4信号の特定の遷移点(0→3、3→0、0→0、3→3)だけを受信データと誤認することで、クロック信号が誤った位置にロックしてしまい、正しくデータが受信できない状況が発生していました(図1)。

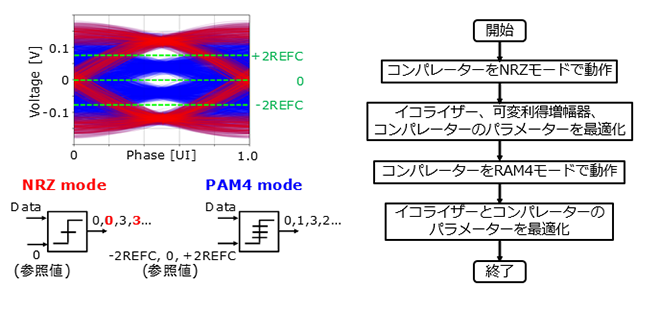

我々は受信信号からクロック信号のロック位置を検出するにあたり、CDR用のコンパレーターをNRZモードで動作させることにより特定の遷移点を見て受信データを誤認することがなくなり、誤ロックが回避できることを発見しました。これを利用して、まずCDR用コンパレーターをNRZモードで動作させてクロック信号を正しい位置でロックさせた後、CDR用コンパレーターをPAM4モードへ変更することによりPAM4信号を正しく受信することが可能となりました(図2)。具体的には、最初にCDR用コンパレーターをNRZモードで動作させた際は、受信機のイコライザー、可変利得増幅器、CDR用及びデータパス用コンパレーターのパラメーターを最適化する制御を行い、クロック信号を正しい位置でロックさせます。CDR用コンパレーターをPAM4モードに切り替えた後にも、イコライザーおよびコンパレーターのパラメーターを最適化する制御を行うことによって、最適な位置にクロック信号をロックさせます。

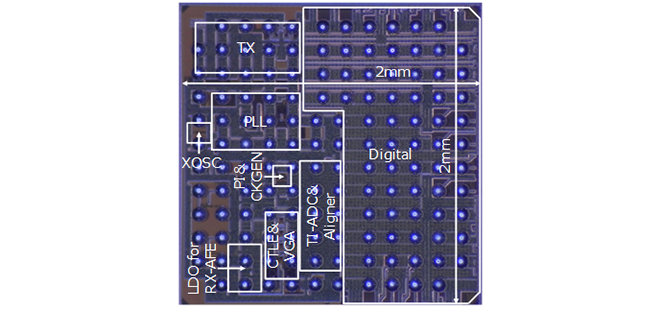

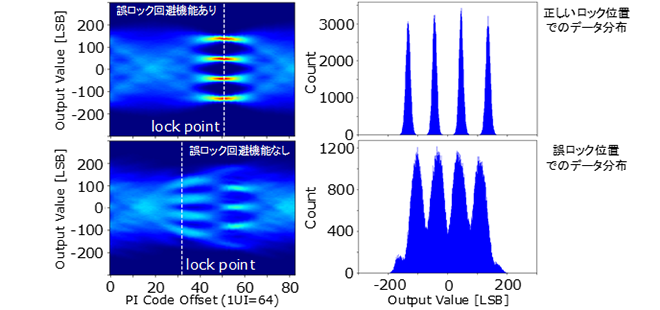

図3に試作したチップ写真を示します。試作したチップは16-nm FinFETプロセスを用いました。試作したトランシーバーの性能評価の際は、トランシーバーの送信機で生成した56GbpsのPAM4信号を一度チップの外部に取り出し、ケーブルを用いてチップ内の受信機にループバックすることにより、56Gbpsでの動作を確認しました。試作したトランシーバーにおいて今回考案した誤ロック回避機能の有効性を確認しました(図4)。

- NRZ:非ゼロ復帰方式(Non Return to Zero)の略称で、1ビットのデータ(0,1)を2つのアナログレベルのパルス信号として伝送する方式です。

- PAM4:4値パルス変調方式(Pulse Amplitude Modulation 4)の略称で、2ビットのデータ(00,01,10,11)を4つのアナログレベルのパルス信号として伝送する方式で、NRZと比較して情報量が2倍となります。

- ADC:アナログデジタル変換器(Analog-to-Digital Converter)の略称で、アナログ信号をデジタル信号に変換する回路です。

- DSP:デジタル信号処理(Digital Signal Processing)の略称で、デジタル信号に対して信号処理を行います。

- ボーレート:1秒間に何回変調するかを示す値です。

- CDR:クロック・データ・リカバリ(Clock and Data Recovery)の略称で、受信したデータ列からクロックやデータを抽出する回路です。

本研究は2022年9月に開催された国際会議ESSCIRC(European Solid-State Circuits Conference)に採択され発表されています[1]。

なお、この成果は国立研究開発法人新エネルギー・産業技術総合開発機構(NEDO)の委託業務の結果得られたものです。

本稿は、文献[1]@2022 IEEEから図面等一部抜粋&再構成したものです。

文献

[1] F. Tachibana et al., “A 56-Gb/s PAM4 Transceiver with False-Lock-Aware Locking Scheme for Mueller-Müller CDR,” in Proceedings of IEEE European Solid-state Circuits Conference (ESSCIRC), pp. 505-508, Sep. 2022.