Please select your location and preferred language where available.

概略

円形セルのコントロールゲート電極(control gate : CG)を分断し半円形状適用により実効セルサイズが縮小できるTwin BiCS FLASHを用いて、さらなるビット密度の増大に有効である、セルの多値動作が可能であることを実証しました。動作最適化により対向セルの独立読出を実現し、導電体電荷蓄積層(floating gate : FG)を用いたセル設計及びFG形状の最適化により、多値動作に重要な広い書込及び消去(program/erase : P/E)ウィンドウ、狭いしきい値電圧(Vth)分布幅、良好なデータ保持特性を実現しました。その結果、ゲート電極分断型セルで4ビット/セル(quadruple-level cell : QLC)及び5ビット/セル(penta-level cell : PLC)動作を実証しました。

緒言

これまでBiCS FLASH™に代表される3次元フラッシュメモリでは、セル積層数を増やし、高アスペクト比の加工プロセスの適用により、低ビットコストかつ大容量という市場要求に応えてきました[1]。しかしセル高積層化が進むにつれ、加工形状制御、寸法の制御、プロセススループットの維持等が難しくなってきています。そこで、従来の円形セルのゲート電極を分断し半円形状適用によりセルサイズを縮小し、少ないセル積層数で高いビット密度を実現するTwin BiCS FLASHを提案し[2]、開発を続けています(図1)。ゲート電極分断型セルには、対向セルのリーク電流及びゲート電極端部のフリンジ電界によるリーク電流起因の読出特性の悪化、セル面積縮小に伴うノイズ特性の悪化という課題がありました。これらの課題をセル動作とセル形状の最適化により克服し、広い書込及び消去ウィンドウと狭いVth分布幅、良好なデータ保持特性を実現しました[3]。

読出動作最適化による対向セル独立読出

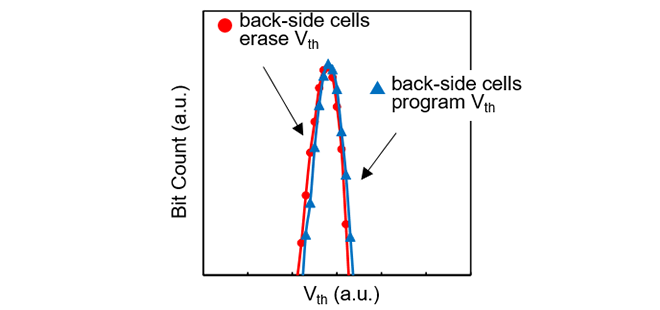

ゲート電極分断型セルは、同一平面上の対向する一対のセルがチャネルSiを共有した構造になっています。そのため対向セルのリーク電流をコントロールできなければ、選択セルの読出が困難になります。そこで読出時に対向セルのゲート印加電圧を最適化することでこの課題を克服しました(図2)。この最適化により、対向するセルが互いのVthの影響を受けずに独立に読出可能であることも確認いたしました(図3)。

導電体電荷蓄積層(FG)形状の最適化による書込、ノイズ、電荷保持特性改善

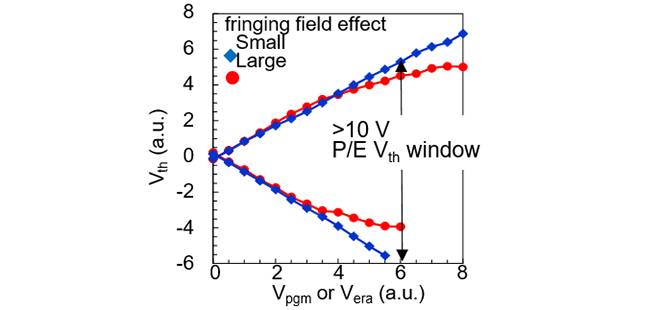

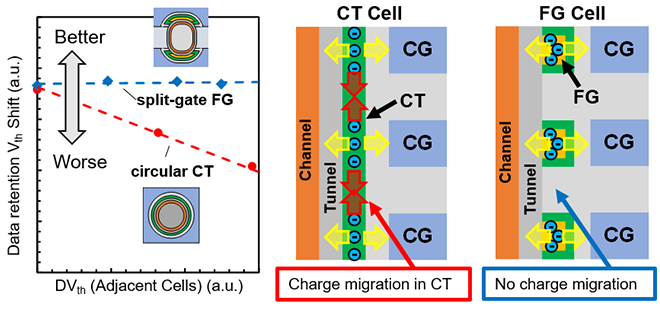

ゲート電極分断型セルでは、ゲート電極端部のフリンジ電界により発生する寄生チャネルを起因とした特性劣化が問題になります。そこでFG形状の最適化によりゲート電界を遮蔽することでリーク電流を制御し、セルサイズを縮小したままで、広い書込消去ウィンドウを実現しました(図4)。また、セルサイズの縮小はランダムテレグラフノイズ(random telegraph noise : RTN)特性を悪化させることが知られておりますが、電荷蓄積層を円形セルで用いられている絶縁性チャージトラップ(charge trap : CT)からFGに変えることで、縮小セルサイズでも円形セルと同等のノイズ特性になることを確認いたしました(図5)。

また、FGセルは電荷蓄積層が各セルで分離されているため、上下セル間で電荷蓄積層がつながっているCTセルと比較してセル間の電荷の移動を抑制することが出来ます。その結果、隣接セルとのVth差によらず電荷保持特性が劣化しないことを確認いたしました(図6)。

ゲート電極分断型セルのQLC、PLC特性

これらの最適化により、ゲート電極分断型セルで4ビット/セル(QLC)及び5ビット/セル(PLC)のVth分布特性を初めて確認することが出来ました(図7)。

まとめ

従来の円形セルのゲート電極を分断した構造を持つTwin BiCS FLASHはセルサイズの縮小に加えて超多値化を実現できるセル構造であり、少ないセル積層数で高いビット密度を達成できる可能性があるセルであることを実証いたしました。

本成果は2022年6月に開催された国際学会2022 IEEE Symposium on VLSI Technology & Circuitsにおいて発表されました。

本稿は、文献[3]@2022 IEEEから図面等一部を抜粋&再構成したものです。

文献

[1] H. Tanaka, et al., “Bit cost scalable technology with punch and plug process for ultra high density flash memory”, Symp. VLSI Tech. Dig., p. 14, 2007.

[2] M. Fujiwara, et al., “3D Semicircular Flash Memory Cell: Novel Split-Gate Technology to Boost Bit Density”, IEDM Tech. Dig., p. 642, 2019.

[3] T. Morooka et al., “Optimal Cell Structure/Operation Design of 3D Semicircular Split-gate Cells for Ultra-high-density Flash Memory”, Symp. VLSI Tech. Dig., p. 308-309, 2022.