Please select your location and preferred language where available.

3次元フラッシュメモリに対して、大容量化、低ビットコスト化、高速化の要求が高まっています。SoC(system on chip)やDRAM(dynamic random access memory)などの他分野の製品に比べて3次元フラッシュメモリは、メモリセルを制御するための高電圧回路が必要なため、微細化、低抵抗化に加えて高耐圧配線技術も求められています。

金属配線材料として多く用いられているタングステンと比較して、銅は比抵抗が低い金属材料です。3次元フラッシュメモリでは、微細配線における銅配線の導入が進んでいます。しかし、銅配線を高電圧回路の微細配線として利用するためには、配線間絶縁信頼性の更なる向上が必要です。そのためには、SiO2層間絶縁膜とSiCNキャップ絶縁膜界面に存在する電荷トラップサイトや欠陥を介した銅イオンのドリフトを抑制することが重要です。

SiCNキャップ絶縁膜と SiO2層間絶縁膜の界面から銅配線を選択的にエッチングして凹状の配線構造を有する銅配線リセス構造を開発しました。本構造により、銅配線間絶縁信頼性が向上することを示すことができました。

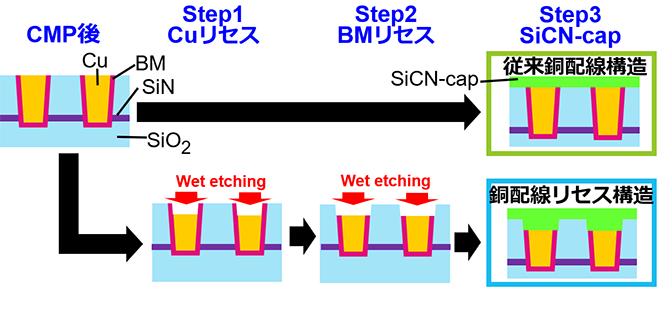

図1に従来の銅ダマシン配線構造と今回検討する銅配線リセス構造を形成するためのプロセスフローを示します。銅配線リセス構造を形成するために、ダマシントレンチRIE(reactive ion etching)の後に、BM(barrier metal)と銅をトレンチ内に充填し、CMP(chemical mechanical polishing)処理を行います。その後、銅とBMを所望の深さまで除去するため、ウェットエッチング工程を追加することにより銅配線リセス構造を実現しました。

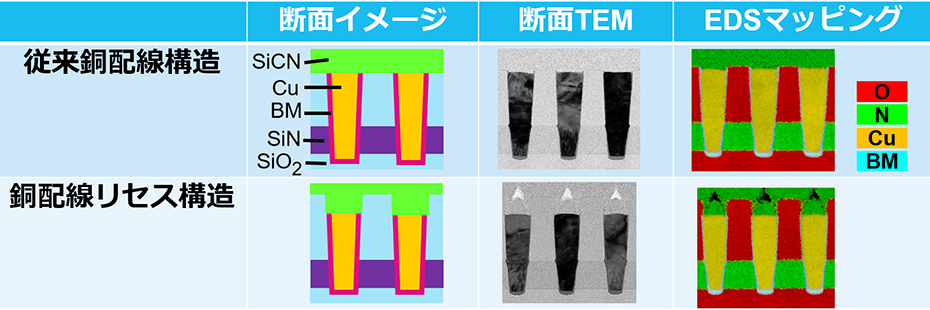

表1に従来銅配線構造と銅配線リセス構造の断面TEM(transmission electron microscope)及びEDS(energy dispersive X-ray spectroscopy)マッピング像を示します。従来銅配線構造は銅とBM最上部がSiO2層間絶縁膜とSiCNキャップ絶縁膜の界面と同じ位置にあります。一方で、銅配線リセス構造は銅とBM最上部がSiCNキャップ絶縁膜とSiO2層間絶縁膜の界面より下方までリセスされています。

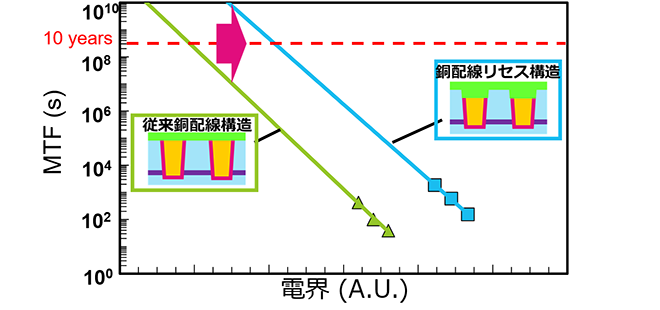

図2に継時的絶縁膜破壊(TDDB : time dependent dielectric breakdown)試験結果を示します。従来銅配線構造と比較して銅配線リセス構造は、50%確率故障時間(MTF : mean time failure)が大きく向上しています。

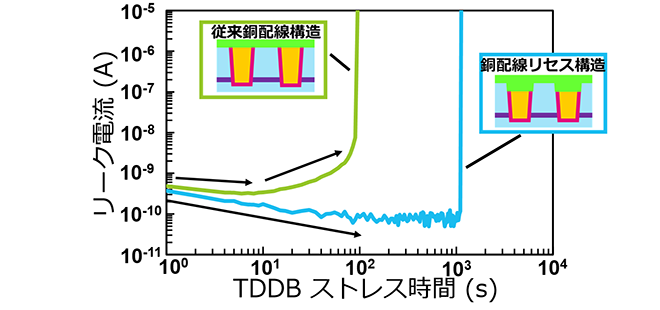

図3にTDDB試験における配線間リーク電流のストレス時間依存性を示します。従来銅配線構造は、電子トラップによるリーク電流減少が発生した後に、銅など陽イオンのドリフトによるリーク電流増加が発生し、絶縁破壊に至っています。一方、銅配線リセス構造は、電子トラップによるリーク電流減少のみ発生した後に絶縁破壊に至っています。

これらの結果から、銅配線リセス構造は、SiO2層間絶縁膜とSiCNキャップ絶縁膜界面に存在する電荷トラップサイトや欠陥を介した銅イオンのドリフトを抑制できた事により、銅配線間絶縁信頼性が向上したと考えられます。よって、銅配線リセス構造は、3次元フラッシュメモリの大容量化と低ビットコスト化と高速化を両立して実現させるために有望であります。

本技術は2022年6月に米国サンノゼにおいて開催された国際学会「IITC 2022 (International Interconnect Technology Conference 2022)」において発表を行いました[1]。

文献

[1] Mitsuhiko Noda et al., "Improvement of Line-to-line TDDB by Cu and Barrier-metal Recess Structure for high voltage circuit in 3D Flash Memory," 2022 IEEE International Interconnect Technology Conference (IITC), 2022, pp. 45-47, doi: 10.1109/IITC52079.2022.9881298.