Please select your location and preferred language where available.

半導体の世界ではムーアの法則に代表されるように最先端の微細化技術を導入することによって年々高密度化を達成してきました。我々の作るフラッシュメモリも微細化と3次元化と共に多値化によって記録密度を向上させています。多値化を行うにはセルの読出しノイズの低減や電荷の保持特性の向上、高耐久性などが求められます。また近年では量子コンピューターの発展などを背景にコンピューターシステムの極低温動作などが求められ、そして低温による半導体素子の特性改善などが報告されています[1]。そこで今回我々は3次元フラッシュメモリ(BiCS FLASH™)の極低温動作を調査し、ストレージ性能の向上を世界で初めて報告しました。

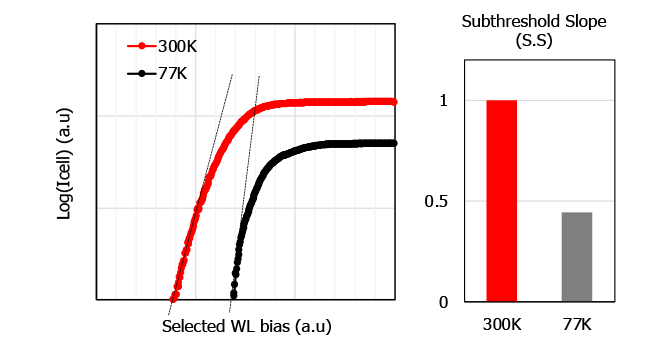

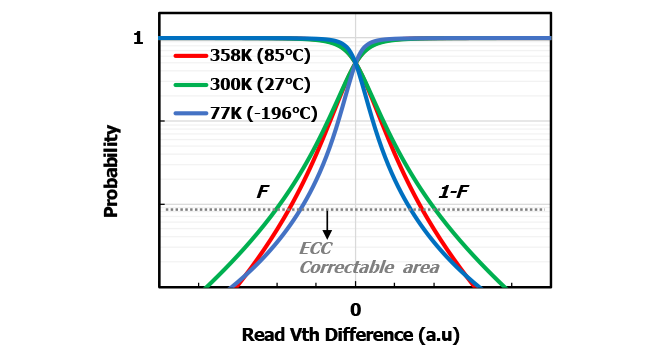

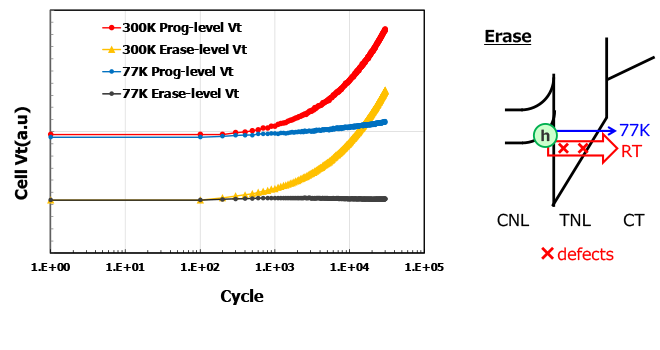

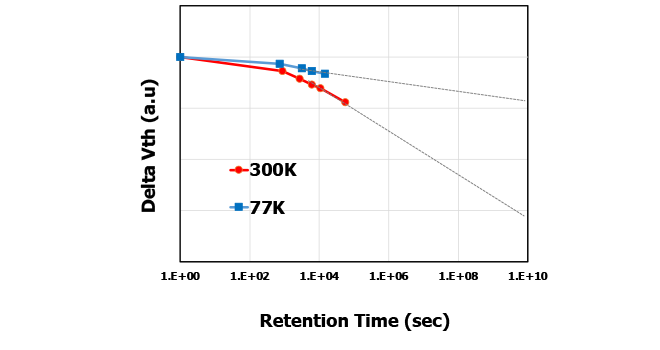

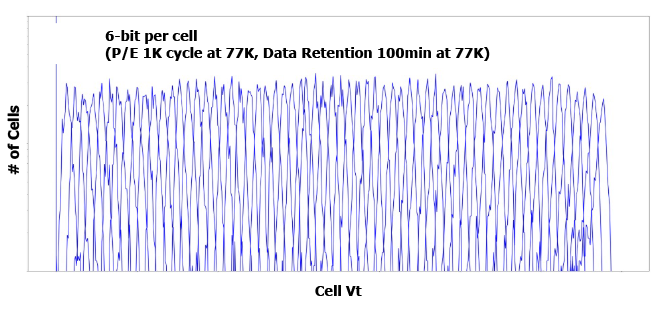

我々の行った実験によると3次元フラッシュメモリは液体窒素温度で動作するだけでなく、I-V特性において急峻なサブスレッショルド特性を示すことを確認しました(図1)。また図2は読み出したセルの閾値分布ですが、液体窒素温度で分布が急峻になっており、読み出しノイズが減っていることがわかります。さらに室温に比べて大きく書き込み/消去サイクル時の閾電圧変動の耐久性が向上しました(図3(a))。これは室温においては熱的な揺動によりトンネル絶縁膜にダメージを与える高エネルギーの正孔が多量に発生しますが、液体窒素温度では発生が少ないためと考えています。また図4はフレッシュ状態のセルの電荷の保持特性ですが、液体窒素温度では室温に比較して良好になっており、トラップされた電荷のデトラップが低温では少ないためと思われます。 これらの良好な素子特性および信頼性によって一つのメモリセルに6ビットのデータを記録する(6bit/cell)の多値化記録動作のデモンストレーションに成功しました(図5)。

本研究は2021年5月に開催された国際会議IMW (International Memory Workshop) に採択され発表しました[2]。また関連した発表を2021年4月に開催された国際会議EDTM (The IEEE Electron Devices Technology and Manufacturing)で行い、ベストペーパーアワードを受賞しました[3]。

[1] G.-H. Lee, D. Min, I. Byun, and J. Kim, "Cryogenic computer architecture modeling with memory-side case studies", Proceedings - International Symposium on Computer Architecture, pp. 774-787

[2] Y. Aiba, H. Tanaka, T. Maeda, K. Sawa, F. Kikushima, M. Miura, T. Fujisawa, M. Matsuo, H. Horii, H. Mukaida, and T. Sanuki, ” Bringing in cryogenics to storage: Characteristics and performance improvement of 3D flash memory”, 2021 IEEE International Memory Workshop, IMW 2021 – Proceedings 9439594

[3] Y. Aiba, H. Tanaka, T. Maeda, K. Sawa, F. Kikushima, M. Miura, T. Fujisawa, M. Matsuo, and T. Sanuki, ” Cryogenic Operation of 3D Flash Memory for New Applications and Bit Cost Scaling with 6-Bit per Cell (HLC) and beyond”, 2021 5th IEEE Electron Devices Technology and Manufacturing Conference, EDTM 2021, 9421051