Please select your location and preferred language where available.

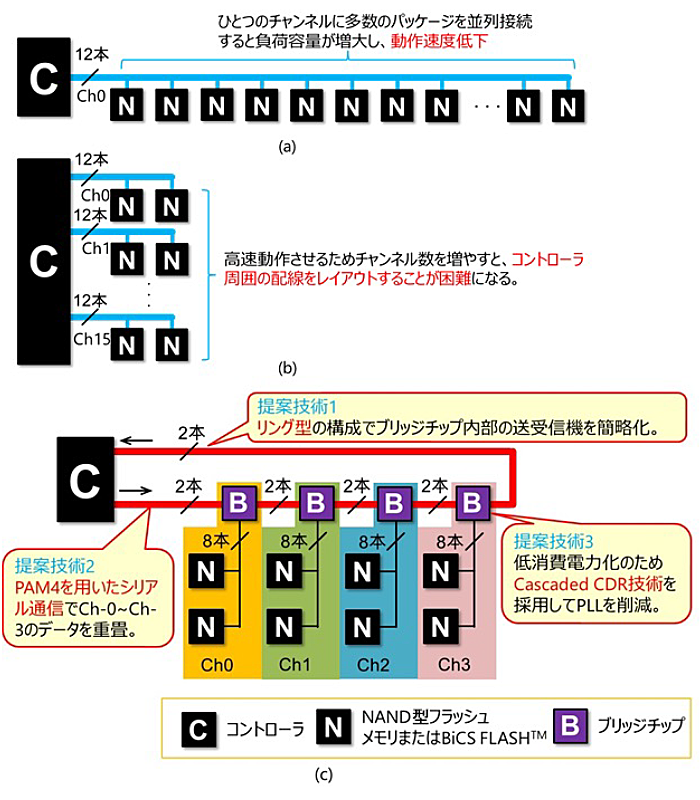

医療や金融など様々な分野でビッグデータが扱われるようになり、高速・大容量のストレージに対するニーズは年々高まっています。NAND型フラッシュメモリおよびBiCS FLASH™(以下NANDと呼ぶ)を使った大容量ストレージを実現するためには、コントローラに多くのNANDを接続する必要がありますが、図1(a)のようにひとつのチャンネルに多数のNANDを接続すると、多数のNANDにより負荷容量が増加し、動作速度が低下します。また、図1(b)のように多数のチャンネルを使って、ひとつのチャンネルあたりに接続されるNANDの数を少なくすると、高速信号線の数が増大し、コントローラ周辺のプリント基板レイアウトが困難になります。

これらの課題を解決するため、図1(c)に示すようにブリッジチップをデイジーチェーン接続*1することにより、少ない高速信号線で多数のNANDを接続し、高速に動作させる手法を考案しました[1,2]。ブリッジチップのチップ面積や消費電力を削減するために下記の3つの技術を開発しました[2]。一つ目はブリッジチップとコントローラをリング状に接続することにより、ブリッジチップ内の送受信機の数を2つから1つに削減する技術、二つ目はPAM4*2を用いたシリアル通信を採用することにより、従来から用いられている0/1の2値を使うNRZ*3信号を用いた場合に比べ、ブリッジチップ内の回路の動作速度を低減させ送受信器に必要となる性能を緩和する技術、最後はブリッジチップ内のCDR*4のジッタ*5特性を改善し、CDRをカスケード接続可能にしたことにより、各ブリッジチップ上のPLL*6回路を省略しチップ面積と消費電流を削減する技術です。

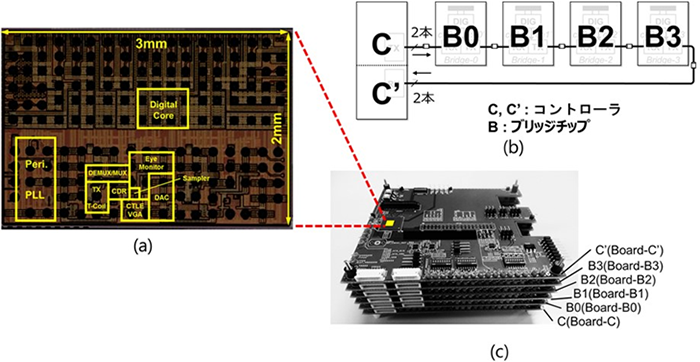

今回開発したブリッジチップのチップ写真を図2(a)に示しますが、チップは28nm-CMOSプロセスを用いて試作しており、評価のためにブリッジチップとコントローラの両方の動作ができるように設計してあります。評価は、図2(b)および(c)に示すように4つのブリッジチップ((B0~B3)と2つコントローラ(CおよびC’)を接続して実施しました。

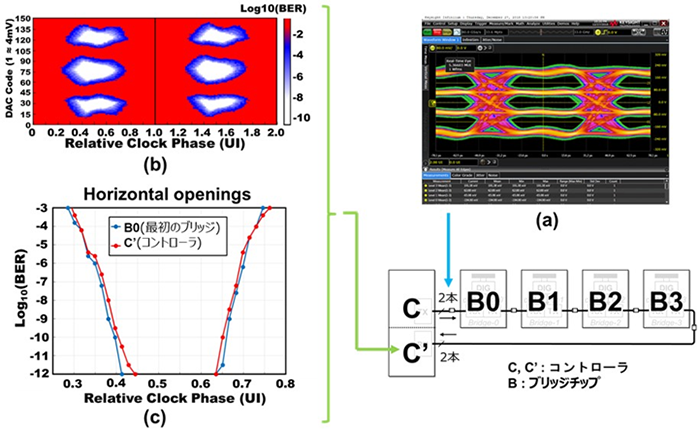

図3(a)はコントローラCとして動作しているチップから出力されたPAM4の送信波形をオシロスコープで測定したもので、良好なPAM4波形が観測されています。この最初のコントローラCから出力されたPAM4信号が4つのブリッジチップを通過し、最後のコントローラC’として動作しているチップに内蔵されたアイモニタで観測されたアイダイアグラム*7を図3(b)に示します。2周期分の波形で、それぞれ3つのクリアなアイ開口が観測されています。図3(c)には1番目のブリッジチップB0と最後のコントローラC’におけるビット誤り率(BER)の実測結果を示します。どちらも10-12以下の良好なビット誤り率が実現されています。同様の評価を全てのブリッジチップとコントローラで行い、良好に25.6GbpsのPAM4通信が行われていることを確認し、将来の高速・大容量のストレージに適用できる可能性を実証しました。

この成果は、2019年2月にサンフランシスコで開催された半導体回路の国際会議「ISSCC 2019 (International Solid-State Circuits Conference 2019)」で発表しました[2]。

- NAND型フラッシュメモリまたはBiCS FLASH™

- デイジーチェーン(Daisy chain):複数のチップを数珠つなぎにする構成

- PAM4: 4値パルス振幅変調

- NRZ(Non-return-to-zero):非ゼロ復帰、0または1の2値の信号を伝送する

- CDR(Clock Data Recovery):受信した信号からデータとクロックを再生すること

- ジッタ(Jitter):クロックや信号波形の時間方向の揺らぎ

- PLL(Phase Locked Loop):基準信号を発生させる回路

- アイダイアグラム(Eye Diagram): 信号波形の遷移を多数サンプリングし、重ね合わせてグラフィカルに表示したもの

【文献】

[1] Y. Tsubouchi, D. Miyashita, Y. Satoh, T. Toi, F. Tachibana, M. Morimoto, J. Wadatsumi, and J. Deguchi, “A 12.8 Gb/s Daisy Chain-Based Downlink I/F Employing Spectrally Compressed Multi-Band Multiplexing for High-Bandwidth and Large-Capacity Storage Systems,” 2018 Symposium on VLSI Circuits, pp. 149-150 (2018)

[2] T. Toi, J. Wadatsumi, H. Kobayashi, Y. Shimizu, Y. Satoh, M. Morimoto, R. Ito, M. Ashida, Y. Tsubouchi, M. Nozawa, G. Urakawa, and J. Deguchi, "A 25.6Gb/s Uplink-Downlink Interface Employing PAM-4-Based 4-Channel Multiplexing and Cascaded CDR Circuits in Ring Topology for High-Bandwidth and Large-Capacity Storage Systems", 2019 IEEE International Solid - State Circuits Conference - (ISSCC), pp. 478-480 (2019)