Please select your location and preferred language where available.

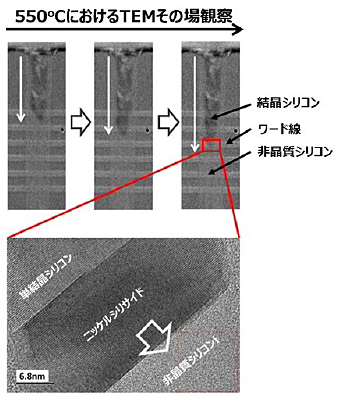

3次元フラッシュメモリの大容量化を実現させるために、ビット高密度化のための高層化技術の開発が進められています。高層化に伴う課題として、チャネル抵抗の増大と多結晶シリコンチャネル(結晶粒界)に起因したセルしきい値のばらつきなどによる性能劣化が挙げられます。この課題を解決する方法の1つとして、シリコンの単結晶化があり、縦型のメモリホールのSiチャネル(マカロニ形状)を単結晶シリコン化する技術の開発を進めています。単結晶化の方法として、TFT(Thin Film Transistor)で検討されている金属(ニッケルシリサイド)を結晶化の成長端とする固相成長技術であるMILC(Metal-induced Lateral Crystallization)に注目しました[1]。我々はこのMILC技術をSiチャネルの結晶化に適用することで、縦型のメモリホールにおいて、ニッケルシリサイドを介して非晶質シリコンからの単結晶形成を実現することができました(図1)。

また、この技術を搭載した3次元フラッシュメモリセル素子で、ポリシリコンをチャネルに用いた従来素子と比べて、優れた電気特性を示しつつ、ばらつきも小さくなることを実証しました(図2)。本技術については、2019年12月に米国サンフランシスコで開催された国際学会「IEDM(International Electron Devices Meeting)」において発表を行いました[2]。

本技術については、2019年12月に米国サンフランシスコで開催された国際学会「IEDM(International Electron Devices Meeting)」において発表を行いました[2]。

[1] S.-W. Lee and S.-K. Joo,” Low temperature poly-si thin-film transistor fabrication by metal-induced lateral crystallization”, IEEE Electron Dev. Lett. 17, pp.160-162 (1996)

[2] H. Miyagawa, H. Kusai, R. Takaishi, T. Kawai, Y. Kamimuta, T. Murakami, K. Ariyoshi, T. Asano, M. Goto, M. Fujiwara, Y. Mitani, T.Obu and H. Aochi, “Metal-Assisted Solid-Phase Crystallization Process for Vertical Monocrystalline Si Channel in 3D Flash Memory”, 2019 IEEE International Electron Devices Meeting, pp.650-653