Please select your location and preferred language where available.

高速・大容量SSD向けPAM4を用いたブリッジチップの開発

- 2019年2月21日

- 東芝メモリ株式会社

当社は、フラッシュメモリを用いた高速・大容量ストレージ(SSD)を実現するためのブリッジチップを開発しました。小面積・低消費電力のブリッジチップを用いることで、ブリッジチップを用いない従来方式より、少ない高速信号線で、より多くのフラッシュメモリを接続することが可能となり、高速化と大容量化の両立が可能になります。本成果はサンフランシスコで開催されている半導体回路の国際会議「ISSCC 2019 (International Solid-State Circuits Conference 2019)」にて、2月20日(現地時間)に発表しました。

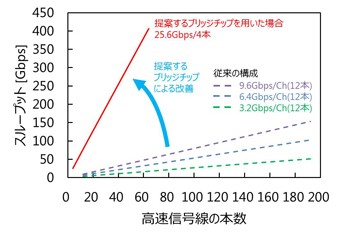

SSDではコントローラに多くのフラッシュメモリが接続されています。ひとつのインターフェイスに多くのフラッシュメモリを接続すると動作速度が低下するため、ひとつのインターフェイスに接続するフラッシュメモリの数は限られます。そのため大容量化には、多数のインターフェイスを用いる必要があり、コントローラと接続する高速信号線の数が膨大になり、配線をSSDの基板上に実装することが困難になります。

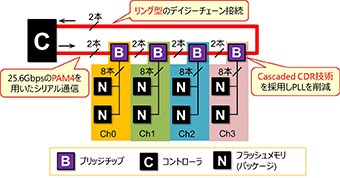

この問題を解決するために、コントローラとフラッシュメモリの間に挿入するブリッジチップを開発しました。また、(1)ブリッジチップとコントローラをリング型のデイジーチェーン(注1)で接続する技術、(2)PAM4(注2)を用いたシリアル通信技術、(3)ブリッジチップのPLL(注3)を不要にするためのジッタ(注4)特性の改善技術を採用する新しい方式(図1)により、ブリッジチップを採用したことによるオーバーヘッドを少なくしつつ、少ない高速信号線で多くのフラッシュメモリを高速に動作させることを可能にしました(図2)。

新しい方式では、ブリッジチップとコントローラをリング型のデイジーチェーン接続することにより、ブリッジチップ内に必要となる送受信器を、2対から1対に削減してブリッジチップのチップ面積を削減しました。また、デイジーチェーン状に接続したコントローラとブリッジチップ間でPAM4を用いたシリアル通信を採用することにより、ブリッジチップ内の回路の動作速度を低減させ送受信器に必要となる性能を緩和しました。さらに、PAM4の特性を利用した新規のCDR(注5)を用いてジッタ特性を改善することにより、ブリッジチップ上のPLLが不要になり、ブリッジチップの面積削減と低消費電力化を実現しました。

今回開発したブリッジチップを28nm CMOSプロセスで試作し、ブリッジチップ4個とコントローラをリング型のデイジーチェーン接続し評価した結果、全てのブリッジチップとコントローラで良好に25.6GbpsのPAM4の通信が行われ、10-12以下のBER(注6)が得られることを確認しました。

今後は、これまでにない高速・大容量のストレージを実現するため、ブリッジチップのさらなる高性能化、小面積化、低消費電力化を目指します。

(注1) デイジーチェーン(Daisy chain):複数のチップを数珠つなぎにする構成

(注2) PAM4(4-level Pulse Amplitude Modulation):4値のデータ転送方式

(注3) PLL(Phase Locked Loop):基準信号を発生させる回路

(注4) ジッタ(Jitter):クロックや信号波形の時間方向の揺らぎ

(注5) CDR(Clock Data Recovery):受信した信号からデータとクロックを再生すること

(注6) BER(Bit Error Rate):ビット誤り率、値が低いほど性能が良い