Please select your location and preferred language where available.

世界初、TSV技術を適用した3次元フラッシュメモリ「BiCS FLASH™」の開発について

- 2017年7月11日

- 東芝メモリ株式会社

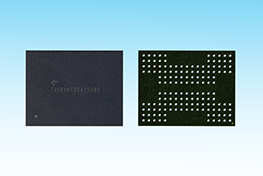

当社は、世界で初めて注1 TSV注2 技術を用いた3ビット/セル(TLC)の3次元フラッシュメモリ「BiCS FLASH™」を試作し、2017年6月から開発用に試作品の提供を開始しました。製品のサンプル出荷は2017年中を予定しています。また、試作品は8月7日から10日まで米国サンタクララで開催される「Flash Memory Summit 2017」で参考展示します。

TSV技術は、複数のチップの内部を垂直に貫通する電極を用いることにより、データ入出力の高速化と消費電力の低減が可能となり、当社は2次元のNAND型フラッシュメモリへの適用実績があります注3。

今回、48層積層プロセスを用いた3次元フラッシュメモリに適用することで、書き込みバンド幅と低消費電力性能の向上に成功し、電力効率注4がワイヤボンディングを用いた製品との比較で約2倍注5 に向上しました。また、512ギガビットのチップをひとつのパッケージ内に16段積層することにより総容量1テラバイトの大容量化を実現しました。

当社は、今後TSV技術を用いた3次元フラッシュメモリ「BiCS FLASH™」の製品化を目指し、アクセス遅延時間の低減、データ転送速度の高速化、単位消費電力あたりの高いIOPS注6 が必要なエンタープライズSSD、フラッシュストレージなどのアプリケーションに大きく貢献します。

試作品の主な仕様

| パッケージタイプ | NAND Dual x8 BGA-152 | ||

|---|---|---|---|

| 記録容量 | 512 GB | 1 TB | |

| 積層数 | 8 | 16 | |

| 外形寸法 | W | 14 mm | 14 mm |

| D | 18 mm | 18 mm | |

| H | 1.35 mm | 1.85 mm | |

| インターフェース規格 | Toggle DDR | ||

| インターフェース最大速度 | 1066Mbps | ||

- 2017年7月11日現在。 当社調べ

- Through Silicon Via:半導体チップの内部を垂直に貫通する電極を用いて複数の半導体チップを1つのパッケージ内で積層する技術

- 世界で初めてTSV技術を用いた最大16段積層NAND型フラッシュメモリの開発について

https://www.kioxia.com/ja-jp/about/news/2015/20150806-1.html - 単位電力当たりのデータ転送量(単位:MB/s/W)

- 当社比

- Input Output Per Secondの略。1秒間に可能なリード、ライトの処理の回数を表すもの。数値が高いほど処理能力が高くなります。

- 本資料に掲載されている情報(製品の価格/仕様、サービスの内容およびお問い合わせ先など)は、発表日現在の情報です。予告なしに変更されることがありますので、あらかじめご了承ください。