Please select your location and preferred language where available.

Technology Topics

Introducing the latest technologies being researched and developed at KIOXIA Corporation and various use cases of flash memories.

Results:1-12 / 32

-

Kioxia, in collaboration with Nanya, developed Oxide-semiconductor Channel Transistor DRAM (OCTRAM) technology. The ultra-low leakage properties of InGaZnO transistors enabled long data retention over 100 sec, providing significant advantages in power saving compared to conventional DRAM.

-

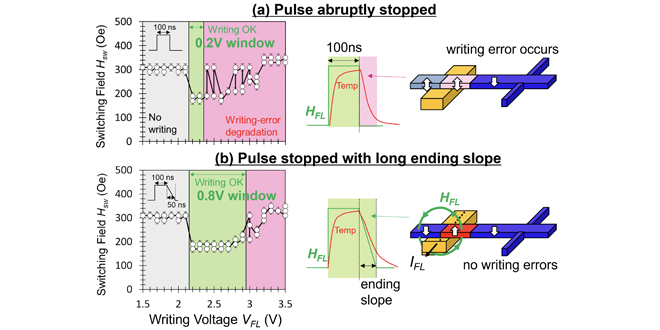

We are developing magnetic domain wall memory as one of the candidates for a new file memory. We have proposed and demonstrated a novel stable writing scheme where writing is performed by the current-induced magnetic field. By gradually stopping the write current pulse, the device is cooled while applying current magnetic field, achieving the stable writing with low error rate. These results were presented in SSDM 2024.

-

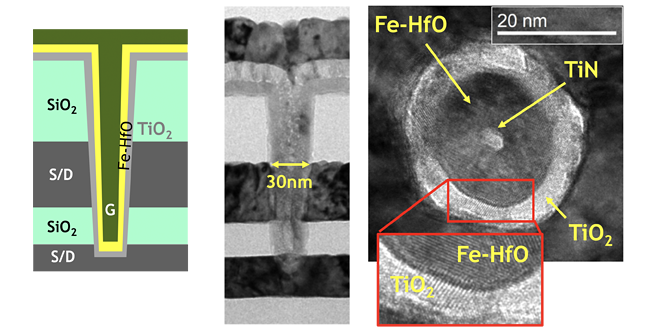

Rapid advances in Artificial Intelligence and Machine Learning are increasing the demand for non-volatile emerging memories with high speed operation. We have demonstrated, for the first time, memory operation of Channel-All-Around FeFET, and realized high ΔIon>2μA and stable endurance (>106cycle) in the smallest footprint ever (707nm2).

-

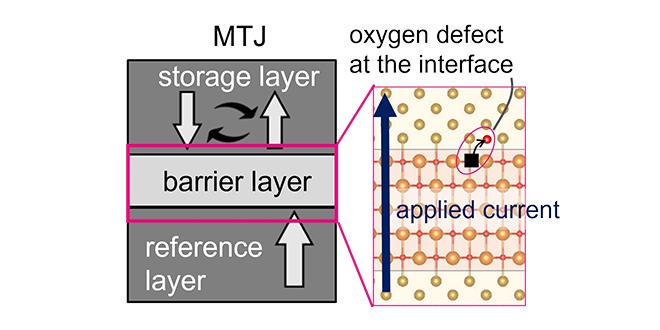

We have investigated the stress-time dependent degradation of magnetic tunnel junction (MTJ) in high-density spin-transfer torque magnetic random access memory (STT-MRAM). We have proposed mechanism and suppression methods of the degradation using the density functional theory calculation and time-evolution model. Our findings provide valuable insights into the reliability in high-density STT-MRAM. This achievement was presented at the IRPS 2024.

-

The limited endurance is one of the major challenges in Si channel FeFET, which has attracted much attention as candidates for next-generation memory. By combining trap-controlled interfacial layer (TCIL) and the charge-control operation sequence, MW of >2 V in FeFET has been achieved even after 107 cycles.

-

We have demonstrated a novel 14nm magnetic tunnel junction(MTJ) for achieving high-retention and high-speed writing simultaneously in 1Z (15-14) nm Spin-Transfer-Torque(STT) MRAM. Our MTJ, called as AccelHR-MTJ(Accelerated STT-Switching and High-Retention MTJ), can show excellent performances such as high-retention of >10 years at 90℃ and high-speed writing down to 5ns. This achievement was presented at the IEDM 2023.

-

Spin orbit torque(SOT) driven magnetization switching has recently attracted attention towards next generation magnetic memory. In this report, we newly introduced a canted bias magnetic field and clarified that it makes the SOT driven perpendicular magnetization switching faster and more stable. This was presented at International Conference on Solid State Devices and Materials in 2023(SSDM2023).

-

We demonstrated a multi-level phase change memory (PCM)/Selector cell which can be programmed without iterative verify operation. Optimal thermal and composition design enabled to form distinct middle resistance state, in which crystalline and amorphous co-exist at designed positions. Multi-level programming was achieved by one single pulse, and it was stable over 107 cycles, making it promising for future cost-effective, large-capacity, and high-speed cross-point memory.

-

HfO2-based Ferroelectric Field-Effect Transistor (FeFET) is a promising candidate for next-generation memory. This study clarified that program/erase cycling generated new trap sites in interfacial SiO2 layer disappears with time. This recovery phenomenon has a non-negligible impact on the threshold voltage behavior during retention process. These results were presented at the international conference SSDM 2023.

-

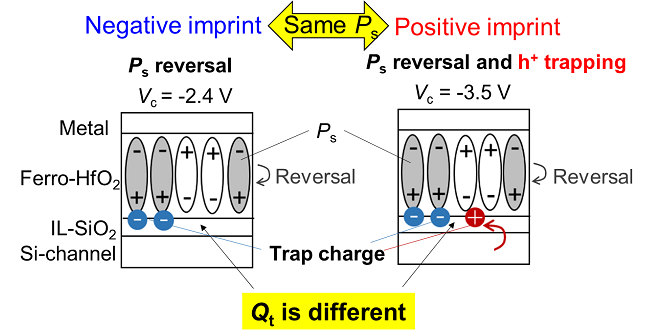

Imprint* is one of the critical reliability challenges in HfO2-FeFET, which has attracted attention as candidates for emerging high-speed memory devices. We have clarified the relationship between spontaneous polarization, trap charge, and imprint by charge component analysis. This result was presented at the international conference SSDM2023.

* Phenomenon in which the voltage required for polarization reversal(coercive voltage Vc) in a ferroelectric film shifts while the polarization state is maintained

-

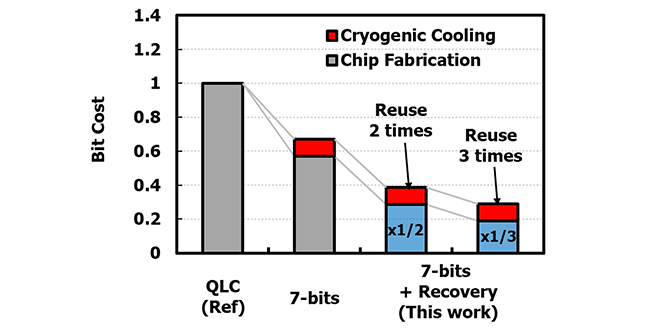

We developed a recovery annealing technology applicable to 7-bit per cell flash memory operating at cryogenic temperatures. The technology can contribute to the realization of a sustainable society through future bit cost scaling and extended chip life.

-

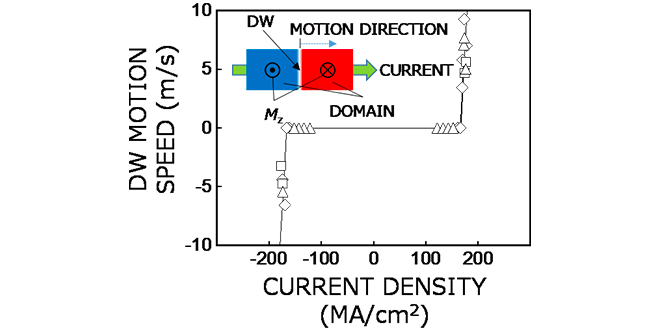

We have successfully demonstrated the preparation of ferromagnetic Co thin layers showing the current-induced domain wall motion (CIDWM), by using atomic layer deposition technique which is widely utilized in the three-dimensional LSI technologies. CIDWM is the key physical phenomenon for race-track memory[1]. This result was presented in the international conference, IEEE INTERMAG 2023[2].

Results:1-12 / 32

R&D Organization

We aim to pursue continuous technological exploration and its social implementation to achieve an affluent and sustainable digitalized society through innovative memory technologies.

Conducts R&D on BiCS FLASH™, a type of 3D flash memory that KIOXIA was the first to develop in the world, while serving as a bridge between R&D and volume production.