Please select your location and preferred language where available.

First demonstration of Channel-All-Around TiO2 Ferroelectric FET for high speed memory application

September 24, 2024

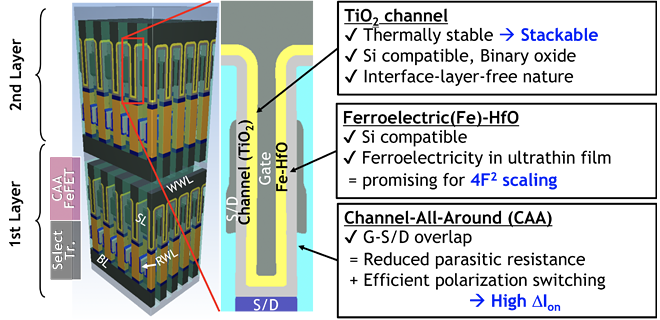

We propose a 3D stackable 4F2 vertical Ferroelectric FET (FeFET) array concept (Figure 1). The key component is TiO2 channel FeFET with Channel-All-Around (CAA) structure. FeFETs with oxide semiconductor channel are known to have better endurance than Si-channel FeFET owing to their interface-layer-free nature[2]. We have demonstrated an excellent endurance over 1e11 cycles with planar TiO2 FeFET[1]. TiO2 channel also has advantages in 3D stackability compared to other OS channels, thanks to its thermal stability.

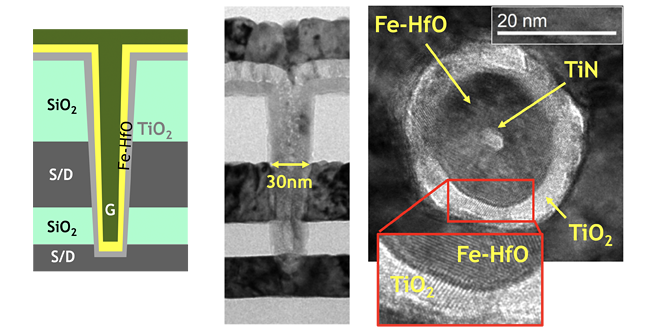

Figure 2 shows TEM images of our CAA FeFET devices. The TiO2/Fe-HfO/TiN stack was formed uniformly on the sidewall of 30nm-diameter hole. It is found that not only Fe-HfO but also TiO2 channel were crystallized, which leads to high thermal stability of the channel against subsequent processes.

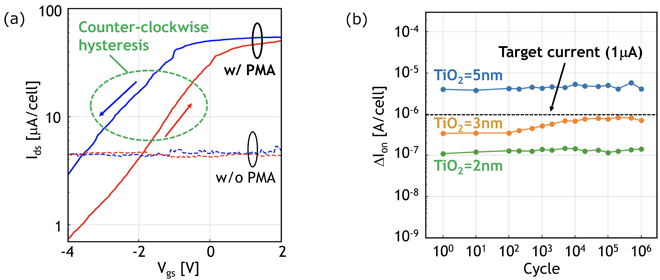

The Id-Vg curve in Figure 3(a) exhibited counter-clockwise hysteresis after PMA, indicating ferroelectric switching. We focus on the change in drain current by polarization reversal (ΔIon) at Vgs=0V, because read operation with Word Line=0V is desirable from the view point of high speed and low power operation. Endurance properties in Figure 3(b) showed stable ΔIon over 1e6 cycles regardless of the TiO2 thickness.

In particular, high drive current (ΔIon > 2μA/cell) and stable endurance were achieved simultaneously in 5-nm-thick TiO2 devices, which has not been achieved in other vertical FeFETs. This work opens a pathway to future 3D stackable 4F2 high speed memory.

This work was presented in the IEEE Symposium on VLSI Technology and Circuits 2024 in Jun. 2024.

Reference

[1] Technology Topics “TiO2 Channel Ferroelectric FET towards High-Performance and Low-Power AI Applications”, May 31, 2023

[2] S. Kabuyanagi et. al., “A Vertical Channel-All-Around FeFET with Thermally Stable Oxide Semiconductor Achieving High ΔIon > 2μA/cell for 3D Stackable 4F2 High Speed Memory”, 2024 IEEE Symposium on VLSI Technology and Circuits, T8-2.