Please select your location and preferred language where available.

High-Endurance FeFET with Metal-Doped Interfacial Layer for Controlled Charge Trapping and Stabilized Polarization

April 09, 2024

FeFET with a ferroelectric HfO as a gate insulator can be programed and erased with high speed and low voltage. And, FeFET has attracted much attention towards a wide range of memory applications such as SCM and file storage. One of the major challenges of FeFET is the limited endurance.

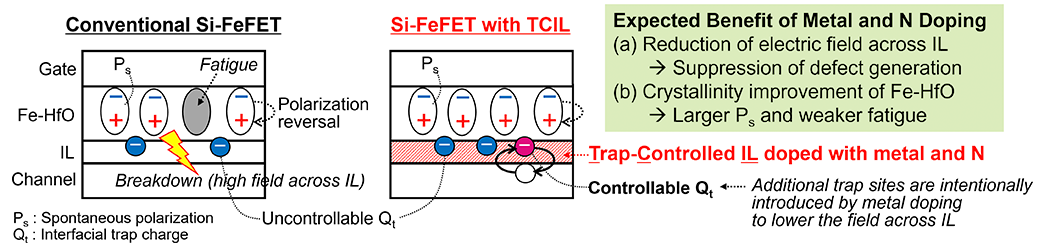

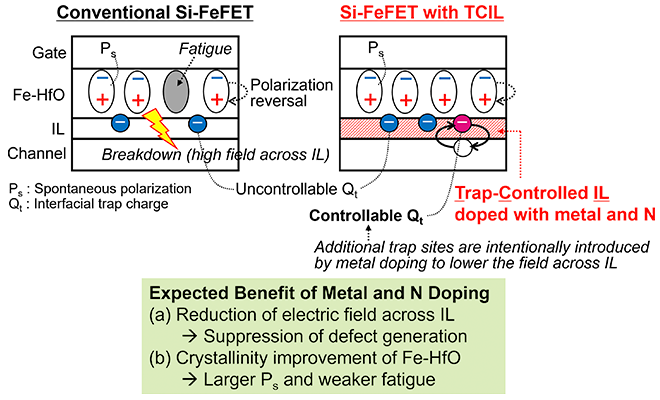

Figure 1 is the concept of this work to improve the endurance. Si channel FeFET has SiO based interfacial layer between the ferroelectric layer and the channel. The degradation of interfacial layer is caused by high electric field across the interfacial layer while cycling. In this work, we suppress the degradation of interfacial layer during cycling by introducing the controlled trap sites intentionally to relax the electric field across interfacial layer. We perform metal and nitrogen doping into the channel-side interfacial layer to form trap-controlled interfacial layer (TCIL).

TCIL also improves the crystallinity of ferroelectric HfO, which results in large spontaneous polarization and weaker fatigue.

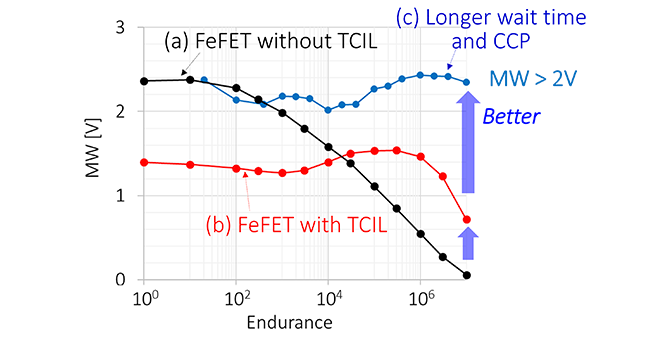

Figure 2 show the cycle dependence of MW in the devices with (Figure 2(b)) and without (Figure 2(a)) metal doping. The device with the TCIL has larger MW after 107 cycles, though initial MW is much smaller since the spontaneous polarization is canceled out by larger amount of trap charges Qt.

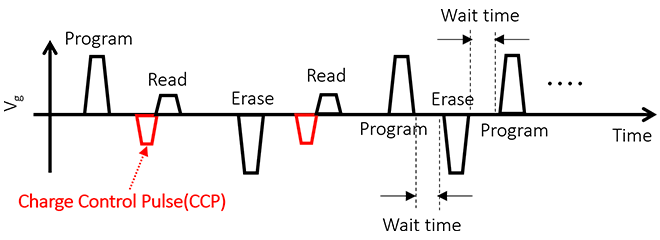

We expand the MW of FeFET with metal-doped TCIL by emitting excessive Qt intentionally by applying Charge Control Pulse(CCP) as shown in Figure 3. By combining TCIL and the charge-control operation sequence such as CCP before readout and long wait time, MW of >2 V has been achieved even after 107 cycles (Figure 2(c)). Charge-controlled FeFET is a viable candidate for various memory applications.

This work was presented in the IEEE International Electron Devices Meeting 2023(IEEE IEDM 2023) in Dec. 2023.

Reference

[1] K. Suzuki et al., “High-Endurance FeFET with Metal-Doped Interfacial Layer for Controlled Charge Trapping and Stabilized Polarization”, IEDM, 35-5 (2023).