Please select your location and preferred language where available.

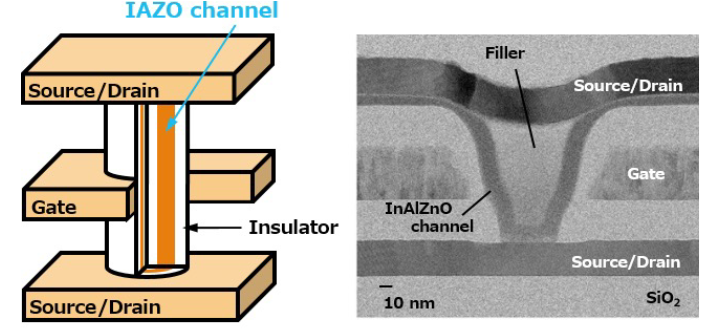

Demonstration of Surrounding gate 3D-Vertical-Channel Transistor Using In-Al-Zn Oxide Channel with Gate Length of 40nm

July 21, 2020

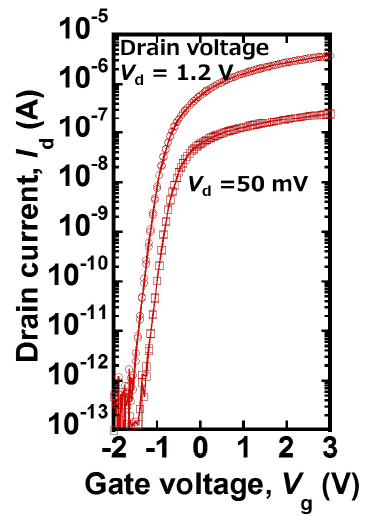

With the coming of 5G era, explosion of high speed mobile devices can be expected. Thus, further downsizing and lower-power consumption characteristic have been strongly demanded to Si-CMOS LSIs. Because of the background, oxide-semiconductor (OS) transistors have attracted much attention due to their advantages: (1) Extremely low-power consumption (Standby power of OS transistors is 10-10 less than that of Si-based transistors), and (2) low cost (Chip size can be shrunk by 3D stack structure on Si-CMOS LSIs by BEOL compatible process).[1]

A challenge of OS-transistor development is improvement of its thermal stability. By using InGaZnO (IGZO) which is a conventional OS, the OS transistor does not work properly by thermal processes required in manufacturing process of the memory device.

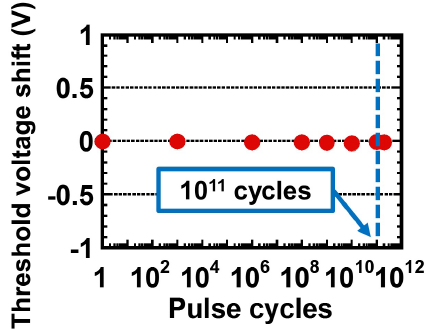

In order to overcome this issue, we have newly proposed InAlZnO (IAZO) as an OS material with high thermal stability. We fabricated a surrounding gate 3D-stackable vertical-OS-channel transistor with gate length of 40nm which can be highly integrated, and successfully demonstrated transistor operation, for the first time. Moreover, endurance over 1011 on/off-cycles was achieved. These results are fundamental technologies for new memory with large amounts of storage, low latency, and ultralow-power consumption and open a path way to realization of new memory device which are never achieved by only silicon-based transistors.

This achievement was presented in the 2020 IEEE VLSI Technology Symposium.[2]

This paper was selected one of the most highlighted papers of VLSI symposia 2020 (Tip Sheet).

[1] M. Oota, Y. Ando, K. Tsuda, T. Koshida, S. Oshita, A. Suzuki, K. Fukushima, S. Nagatsuka, T. Onuki, R. Hodo, T. Ikeda, and S. Yamazaki, “3D-Stacked CAAC-In-Ga-Zn Oxide FETs with Gate Length of 72nm”, 2019 IEEE IEDM, pp.50-53.

[2] H. Fujiwara, Y. Sato, N. Saito, T. Ueda, and K. Ikeda, 2020 IEEE Symposium on VLSI Technology, TH2.2.